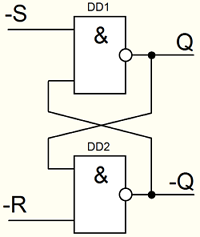

Всем доброго времени суток! Сегодняшний мой пост посвящён цифровым микросхемам, которые имеют память. Подобно тому, как человек помнит события из своей жизни, так и эти микросхемы могут долго хранить заложенную в них информацию, а когда необходимо выдавать её. Такими цифровыми микросхемами являются триггеры (англ. – Trigger или Flip-Flop). В отличие от простых логических микросхем, которые называют комбинационными (НЕ, И-НЕ, ИЛИ и другие) и их сигналы на выходе чётко соответствуют сигналам на входе, то триггеры относятся к последовательным или последовательностным микросхемам, уровень выходного напряжения которых, зависит от того в какой последовательности поступали сигналы на вход триггера. С помощью триггеров строят более сложные цифровые микросхемы. Сигналы, поступившие на вход триггера, могут храниться только до тех пор, пока на него подается напряжение питания. После каждого включения триггера на его выходах появляются случайные логические уровни напряжения. Триггеры обладают очень высоким быстродействием, сравнимым с задержками при переключении простейших логических элементов, однако объём хранимой информации мал. Один триггер может хранить только один сигнал или бит. Не вдаваясь в глубину схемотехники триггера, скажу сразу, что простейший триггер представляет собой схему из двух логических элементов, взаимодействуя между собой с помощью положительной обратной связи, которая обеспечивает нахождения выходов триггера в одном их двух логических состояний неограниченное время. Схема на рисунке выше представляет простейший триггер (или триггерная ячейка), который имеет два входа и два выхода. Входы триггера реагируют на низкий логический уровень: вход R – сброс (англ. Reset – сброс) и вход S – установка (англ. Set – установка), выходы: прямой Q (англ. Quit – выход) и инверсный –Q. Как говорилось выше, входы триггера R и S реагируют на низкий логический уровень и сигналы на них должны поступать с некоторой разницей во времени. Опишем работу данной схемы. Когда на обоих входах триггера присутствует низкий логический уровень, то это никак не отразится на уровне напряжения на выходах. Когда на вход S поступит сигнал лог. 1, то на выходах Q будет лог. 0, а на –Q – лог. 1. Если теперь на вход R триггера поступит лог. 1, то выходные сигналы не изменятся. И наконец если изменить уровень сигнала на входе S с высокого на низкий уровень, то на выходе триггера Q будет лог. 1, а на –Q – лог. 0. Таким образом, для данной триггерной ячейки можно составить таблицу истинности. Схемы с такой таблицей истинности называются RS триггерами. RS триггеры служат основой для многих динамических устройств: делители частоты, счётчики, регистры. Кроме вышеописанного RS триггера существует ещё несколько типов триггеров, которые отличаются методом управления, входными и выходными сигналами. Все современные триггеры объединены в серии цифровых микросхем: Рассмотрим принцип работы RS триггера возьмём микросхему К555ТР2. Данная микросхема имеет 4 RS триггера, два из которых имеют по одному R входу и одному S входу, а два других – по одному R входу и по два S входа, объединенных по функции И. Все 4 RS триггера данной микросхемы имеют по одному прямому выходу. Принцип работы данных триггеров не отличатся от триггерной ячейки описанной выше. Импульс с низким уровнем на входе триггера R приводит состояние выхода к низкому уровню, а импульс с низким логическим уровнем на входе триггера S – состояние выхода в высоком логическом уровне. В случае появления одновременных сигналов на входах триггера переводит его выход в состояние лог. 1, а после окончания импульсов в одно из устойчивых состояний. Микросхема типа К555ТВ9, является представителем семейства JK триггеров, который имеет следующий принцип работы. Микросхема К555ТВ9 содержит два JK триггера. Триггеры данного типа сложнее по устройству и по управлению по сравнению с RS триггером. В дополнение к стандартным входам R и S, которые работают аналогично с RS триггером, в JK триггере имеются информационные входа J и K, а также вход синхронизации С. Принцип работы JK триггера следующий. Вход R триггера служит для перевода прямого выхода в лог.1, а вход S триггера – в состояние лог.0. Вход С (англ. Clock – часы)служит для тактирования JK триггера, то есть все изменения выходов происходят только когда на входе С сигнал изменяется с высокого уровня на низкий. Информационные входа J (англ. Jump – прыжок) и К (англ. Kill – убить) работают следующим образом: если на J лог.1 и на К лог.0, то по импульсу со входа С на Q будет лог.1 и на –Q будет лог.0. Для изменения уровня сигнала на выходах на противоположные необходимо на J подать лог.0, а на К лог.1, тогда по импульсу на входе С состояние выходов измениться. D триггер является самым используемым, а по управлению он занимает промежуточное положение между RS триггером и JK триггером. Представителем D триггеров является микросхема К555ТМ2. В составе данной микросхемы содержится два D триггера, которые имеют два входа сброса и установки R и C, информационный вход D (англ. Dalay – задержка) триггера и один тактируемый вход С триггера, а также два выхода: прямой Q и инверсный –Q. Как и все триггеры, у которых имеется тактируемый вход С, принцип работы D триггера основан на переключении уровней напряжений на выходе триггера только стробированием по входу С. Таким образом можно составить таблицу истинности D триггера. D триггер является наиболее универсальным потому, что данным триггером можно заменить все остальные RS триггеры и JK триггеры. Для замены RS триггера необходимо просто не использовать входы D и C входы D триггера, а относительно JK триггера, то для большинства схем одной пары входов вполне достаточно. Ниже приведены схемы замены триггеров Теория это хорошо, но теория без практики - это просто сотрясание воздуха. Перейдя по ссылке всё это можно сделать своими руками Скажи спасибо автору нажми на кнопку социальной сети www.electronicsblog.ru ФЕДЕРАЛЬНОЕ АГЕНТСТВО ПО ОБРАЗОВАНИЮ Федеральное государственное образовательное учреждение высшего профессионального образования «ЮЖНЫЙ ФЕДЕРАЛЬНЫЙ УНИВЕРСИТЕТ» Лабораторная работа № ____ ТРИГГЕРНЫЕ СХЕМЫ Доцент кафедры радиофизики Кулешов Г.И. Ростов-на-Дону 2008 ВВЕДЕНИЕ Триггерные схемы относятся к классу последовательностных устройств, отличительной особенностью которых является зависимость их текущего состояния от значений управляющих сигналов в предшествующие моменты времени, чем обеспечивается возможность выполнения функций запоминания и хранения информации. Они строятся на основе комбинационных логических схем. Исследование работы триггерных схем выполняется на специализированном лабораторном макете “ОСНОВЫ ЦИФРОВОЙ ТЕХНИКИ” с использованием сменного центрального блока “ОСНОВЫ ЦИФРОВОЙ ТЕХНИКИ”. В качестве дополнительных источников входных сигналов используются элементы левого блока, для индикации состояния исследуемых устройств используются элементы “КОНТРОЛЬ ВЫХОДА” и “СЧЕТЧИК ИМПУЛЬСОВ” правого блока лабораторного макета. В настоящей работе для описания работы схем используется положительная логика. ЦЕЛЬ РАБОТЫ: Изучение устройства и принципов функционирования основных типов триггерных схем. 1.1. Асинхронные триггеры Общая структура триггера представлена на рис. 1. Она содержит ячейку с двумя устойчивыми состояниями (бистабильную ячейку) и схему управления. Штриховой линией показана цепь обратной связи – передача сигналов с выхода на вход устройства. Рис. 1.1. Общая структура триггера. Бистабильная ячейка может быть реализована на элементах 2ИЛИ-НЕ, либо на элементах 2И-НЕ. Схема, показанная на рис. 1.2, состоит из двух элементов 2ИЛИ-НЕ, включенных последовательно и охваченных положительной обратной связью. Для нее при низких уровнях на входах S и R (Set – установка, Reset – сброс) выполняется условие генерации на нулевой частоте. Выходной сигнал (логический 0 или 1) проходит последовательно два инвертора и возвращается в точку начала обхода схемы с тем же уровнем (0 или 1). Рис. 1.2. Принципиальная схема асинхронного RS-триггера на элементах 2ИЛИ-НЕ (дизъюнктивная бистабильная ячейка). Два низких уровня на входах S и R соответствуют режиму хранения информации, записанной в триггер. Установка триггера () производится подачей высокого уровня (импульса) на входS. Положительный импульс на входе S (Set – установка) приводит к появлению на инверсном выходе низкого уровня, на прямом выходе высокого. Считается, что в триггер записана единица, или триггер установлен (в единичное состояние, определяемое по уровню сигнала на прямом выходе ). После окончания переходных процессов в схеме и установления на прямом выходе высокого уровня, который является дублирующим для сигнала S установки, сигнал S может быть переведен в низкий уровень, и триггер будет находиться далее в режиме хранения. Схема симметричная, поэтому положительный импульс на входе R приводит к появлению на прямом выходе низкого уровня, на инверсном выходе высокого. Считается, что в триггер записан ноль, или триггер сброшен. Два высоких уровня на входах S и R, действующих одновременно, представляют запрещенное состояние триггера, так как при переходе из него в режим хранения информация в триггере может стать неопределенной. Состояние триггеров описывается с разделением времени на дискретные интервалы, последовательным моментам времени приписываются индексы n и n+1. Для асинхронных триггеров разделение времени в значительной степени произвольно, однако должны выдерживаться интервалы времени, достаточные для процессов переключения элементов схемы. В более сложных синхронных устройствах дискретные интервалы времени естественным образом связаны с периодом следования синхронизирующих тактовых импульсов. Для формального описания функционирования триггеров используется полная или сокращенная таблица состояний. Полная таблица состояний Сокращенная таблица состояний Sn Rn Qn+1 __ Qn+1 0 0 0 1 1 0 1 1 Qn 0 1 Z __ Qn 1 0 Z Sn Rn Qn+1 0 0 0 1 1 0 Qn 0 1 В полной таблице для запрещенных комбинаций состояний входных сигналов, вызывающих запрещенное состояние триггера, выходные сигналы обозначены знаком Z. В сокращенной таблице запрещенные комбинации не указываются, состояние инверсного выхода также не приводится. Диаграммы работы в различных режимах RS-триггера на элементах 2ИЛИ-НЕ показаны на рис. 1.3. Рис. 1.3. Временные диаграммы работы RS-триггера на элементах 2ИЛИ-НЕ. Асинхронный триггер может быть построен на элементах 2И-НЕ по схеме, приведенной на рис. 1.4. Наличие двух устойчивых состояний также обеспечивается положительной обратной связью. Режим хранения соответствует подаче на входы двух высоких уровней. Рис. 1.4. Принципиальная схема асинхронного RS-триггера на элементах 2И-НЕ (конъюнктивная бистабильная ячейка). Установка триггера (запись 1 на выход Q) производится подачей низкого уровня (отрицательного импульса) на вход , сброс (запись 0 на выходQ) осуществляется подачей низкого уровня (отрицательного импульса) на вход . Два низких уровня на управляющих входах являются запрещенным состоянием. Полная таблица состояний триггера имеет следующий вид: Детальное представление временных соотношений в RS-триггере показано на рис. 1.5. Рис. 1.5. Временные диаграммы работы RS-триггера на элементах 2И-НЕ с указанием интервалов времени переключения логических элементов. Отмечены интервалы времени, в которые происходят процессы переключения в логический элементах, составляющих триггер. Диаграммы работы в различных режимах RS-триггера на элементах 2И-НЕ приведены на рис. 1.6. Рис. 1.6. Временные диаграммы работы RS-триггера на элементах 2И-НЕ. На принципиальных электрических схемах RS-триггеры обозначаются согласно рис. 1.7. Рис. 1.7. Обозначение асинхронных RS триггеров на принципиальных электрических схемах. Асинхронные RS-триггеры могут быть использованы для формирования импульсных сигналов при переключениях механических контактов. Замыкание и размыкание контактов сопровождается “дребезгом”, т.е. многократным переключением уровней сигналов за время порядка 1 мс. Причиной являются механические колебания упругих элементов конструкции переключателей. Схема, обеспечивающая формирование одного перепада напряжения по нажатию кнопки и одного по отпусканию, показана на рис. 1.8. В ней при верхнем положении подключенного к нулевому проводу подвижного контакта реализуется режим установки триггера. При размыкании контакта триггер переходит в режим хранения и при повторных замыканиях обратно в режим установки, состояние выходов не меняется. После перемещения подвижного контакта к нижнему и первого замыкания триггер сбрасывается, формируется отрицательный перепад напряжения на прямом выходе (и положительный на инверсном выходе) триггера. Дребезг приводит к переходу в режим хранения и повторным сбросам. При отпускании кнопки подвижный контакт возвращается в верхнее положение, вследствие симметрии схемы происходят аналогичные процессы и формируется один перепад выходного напряжения. Рис. 1.8. Антидребезговая схема. Схема рис. 1.8 предназначена для выполнения на элементах ТТЛ-логики, аналогичные устройства применяются при работе с КМОП-логикой. 1.2. Синхронные триггеры В рассмотренных схемах изменение входных сигналов возможно в произвольные моменты времени. Сложные устройства строятся с применением синхронизации. Схема синхронизируемого уровнем RS-триггера показана на рис. 1.9. Изменения состояния выходов триггера (сброс и установка) возможны только во время действия положительного уровня на входе С, предназначенного для подачи синхронизирующих сигналов. Диаграммы работы триггера приведены на рис. 1.10. а) б) Рис. 1.9. Статический синхронизируемый уровнем RS-триггер на элементах 2И-НЕ. а) Схема электрическая принципиальная. б) Условное графическое обозначение. Рис. 1.10. Временные диаграммы работы статического синхронизируемого уровнем RS-триггера на элементах 2И-НЕ. Недостатком схемы является наличие “прозрачного” режима работы, т.е. во время действия положительного уровня сигнала синхронизации при многократном изменении управляющих сигналов соответственно изменяются выходные сигналы. Для обеспечения однократной передачи изменения сигналов на выходы триггера при прохождении синхроимпульса применяются двухступенчатые схемы триггеров структуры Ведущий – Ведомый (Мастер – Помощник). Схема триггера показана на рис. 1.11. Для правильной работы триггера время задержки распространения элемента DD9 должно быть меньше, чем время процессов установления сигналов в ведущем триггере. Рис. 1.11. Двухступенчатый триггер (MS-триггер). Второй вариант – напряжение квантования элемента DD9 должно быть меньше, чем у элементов DD1 и DD2. Тогда при подаче положительного синхроимпульса происходит отключение связи между ведущим и ведомым триггерами, запись информации в ведущий триггер. При поступлении отрицательного перепада синхроимпульса выполняется отключение элемента памяти ведущего триггера от управляющих входов и затем разрешается управление ведомым триггером и передача в него информации из ведущего триггера. Этот триггер также имеет запрещенное состояние – два высоких уровня на входах R и S. Однако он может работать в схемах с внешними обратными связями. Если соединить прямой выход и вход сброса, а также инверсный выход и вход установки, то схема будет работать в счетном режиме, при котором по каждому синхроимпульсу состояние выходов меняется на противоположное. Таким способом выполняется деление частоты входного синхросигнала в два раза. Триггер в счетном режиме имеет название T-триггер. Применением дополнительной логики в цепях подачи управляющих сигналов можно обеспечить полное управление функционированием триггера и исключить запрещенные состояния. На рис. 1.12 показана схема JK-триггера, построенная на базе MS-триггера. Рис. 1.12. JK-триггер на базе MS-триггера. Низкие уровни сигналов на входах J и K запрещают переключения элементов схемы и обеспечивают режим хранения информации. Установка триггера разрешается высоким уровнем на входе J, сброс выхода в нулевое состояние разрешается высоким уровнем на входе K. При подаче двух высоких уровней на входы J и K одновременно триггер работает в счетном режиме. Реальные микросхемы имеют по несколько управляющих входов, объединенных логикой И, для применения в более сложных схемах. На рис. 1.13 показана схема JK-триггера, построенная с применением элементов, обеспечивающих задержку сигналов. Рис. 1.13. Принципиальная схема JK-триггера на элементах с внутренней задержкой. Одной из распространенных задач, решаемых с помощью триггера, является хранение одного бита информации (значения 0 или 1). Специальная схема имеет название D-триггер. Она может быть получена из схемы статического синхронизируемого уровнем RS-триггера, если соединить через инвертор управляющие входы, как показано на рис. 1.14. В этой схеме при подаче положительного уровня на вход синхронизации происходит запись бита информации со входа D, и после переключения синхросигнала в низкий уровень хранение информации. Схема на рис. 1.14 является избыточной, такие же функции можно выполнить с применением четырех элементов, как показано на рис. 1.15 (триггер-защелка). Недостаток схемы – наличие прозрачного режима – компенсируется простотой схемы, чем обеспечивается ее широкое применение на практике для хранения данных. Рис. 1.14. Принципиальная схема статического D-триггера на основе статического RS-триггера. Рис. 1.15. Построение схемы статического D-триггера на четырех элементах 2И-НЕ. Схема электрическая принципиальная и условное графическое обозначение. 1.3. Динамические триггеры Разработаны и широко используются схемы различных триггеров, переключающихся в моменты времени, непосредственно близкие к фронтам синхроимпульсов, и не реагирующих на изменения управляющих сигналов в остальные моменты, – динамические триггеры. Они не имеют “прозрачного” режима. Схема шестиэлементного динамического D-триггера показана на рис. 1.16. Она состоит из трех триггеров с дополнительными связями. На условном графическом обозначении вход синхронизации отмечен наклонной черточкой, это показывает, что запись информации происходит по положительному перепаду (фронту) синхроимпульса. Линия противоположного наклона на обозначениях других динамических триггеров соответствует срабатыванию по отрицательному перепаду (срезу) синхроимпульса. а) б) Рис. 1.16. Динамический D-триггер. а) Схема электрическая принципиальная. б) Условное графическое обозначение. Схема работает следующим образом. Режиму хранения информации соответствует низкий уровень на входе синхронизации (C = 0). Тогда X2 = 1, X3 = 1. Триггер на элементах DD5, DD6 находится в режиме хранения, выходные сигналы ине меняются. На верхний вход элементаDD1 приходит сигнал X2 = 1, следовательно, его выходной сигнал . На нижнем входе элементаDD4 действует сигнал X3 = 1, на его выходе . Поэтому во время действия сигналаC = 0 один из внутренних триггеров, DD1-DD2 или DD3-DD4 , находится в “неправильном” (“запрещенном”) состоянии. Если D = 0, тогда DD1-DD2, при D = 1 – триггер DD3-DD4. После переключения сигнала синхронизации в высокий уровень “неправильное” состояние одного из внутренних триггеров исчезает (по крайней мере, до изменения сигнала D). Переключение выходных уровней ивозможно сразу после изменения синхросигнала с низкого уровня на высокий (при прохождении положительного перепада на входC). Последовательность изменения состояний схемы зависит от уровня сигнала D. Если в момент прихода положительного перепада синхроимпульса действует сигнал D = 0 , то сразу после установления C = 1 схема переключается в состояние X1 = 1, X2 = 0, X4 = 0, X3 = 1. Триггер на элементах DD5, DD6 сигналом сброса переключается в состояниеи. ЭлементDD1 блокируется сигналом X2 = 0, и до тех пор, пока C = 1, независимо от последующих изменений сигнала D, состояние выходов всех логических элементов не меняется. При уровне D = 1 в момент прихода положительного перепада синхроимпульса сразу после установления C = 1 схема переключается в состояние X1 = 0, X2 = 1, X4 = 1, X3 = 0. Триггер на элементах DD5, DD6 сигналом установки переключается в состояниеи. ЭлементыDD4 и DD2 блокируются сигналом X3 = 0, и пока C = 1, независимо от последующих изменений сигнала D, состояние выходов логических элементов DD2, DD3, DD4, DD5 () иDD6 () не меняется. Сигнал (вследствие действия X2 = 1), и при C = 1 может принимать значения 0 либо 1. В рассматриваемой схеме переключение выходных сигналов происходит не более, чем один раз на каждый синхроимпульс (по его положительному перепаду), с задержкой на время распространения в соединяющих вход с выходом внутри триггера логических элементах. Задержка достаточна для того, чтобы к моменту переключения выходов вход D был заблокирован, и чтобы схема не реагировала на изменения сигнала D до переключения входа C в низкий уровень. Поэтому динамический D-триггер может работать в схемах с внешними обратными связями. При соединении инверсного выхода с входом данныхD по положительному перепаду (фронту) каждого синхроимпульса состояние триггера изменяется на противоположное, т.е. частота выходных импульсов вдвое меньше частоты входных. Это счетный режим работы D-триггера. Указанным соединением выполняется преобразование динамического D-триггера в T-триггер. studfiles.net Аннотация: Рассматривается принцип действия триггеров как простейших элементов электронной памяти. Цифровое устройство называется последовательностным [1, с.91], если его выходные сигналы зависят не только от текущих значений входных сигналов, но и от последовательности значений входных сигналов, поступивших на входы в предшествующие моменты времени. Поэтому говорят, что такие функциональные узлы "обладают памятью". Триггер - это логическая схема с положительной обратной связью, которая может находиться только в одном из двух устойчивых состояний, принимаемых за состояние логического нуля и логической единицы. В отличие от всех рассмотренных ранее комбинационных схем, работа которых определяется только входными сигналами, состояние триггера в текущий момент зависит и от его состояния в предыдущий момент времени. Иными словами, триггер - это схема с запоминанием [2]. Простейшая функциональная схема RS - триггера в базисе ИЛИ-НЕ приведена на рис. 7.1,а. Здесь Очевидно, при наличии двух входных сигналов, возможны 4 варианта работы схемы (табл. 7.1). Начнем анализ с состояний, когда на один из входов подается решающий для элемента ИЛИ-НЕ сигнал логической 1. Первая такая комбинация: Вторая комбинация: Если на оба входа подать Рассмотрим последнюю, четвертую комбинацию входных сигналов: Для рассматриваемой схемы характерно также и то, что оба элемента триггера переключаются не одновременно, а последовательно друг за другом. Поэтому в ходе переходного процесса переключения триггера в противоположное состояние будут моменты времени, когда и на прямом, и на инверсном выходах будут одинаковые уровни. Это недопустимо по определению, поскольку триггер должен быть либо в устойчивом состоянии логического Функциональная схема простейшего триггера в базисе И-НЕ показана на рис. 7.2.а. Поскольку для функции И-НЕ решающим является сигнал логического нуля, активный уровень входных сигналов будет нулевым (табл. 7.2), что отражается на УГО триггера (рис. 7.2,б) в виде инверсного изображения входов Основное назначение триггера в цифровых схемах - хранить выработанные логическими схемами результаты. Для отсечения еще не установившихся, искаженных переходными процессами результатов между выходом какой-либо логической схемы и входами триггера ставят ключи в виде элементов И-НЕ. Действие этого сигнала аналогично разрешающему сигналу Недостатком схемы остается наличие недопустимой комбинации на входе, при которой получается неустойчивое состояние схемы. www.intuit.ru Материал из Национальной библиотеки им. Н. Э. БауманаПоследнее изменение этой страницы: 17:36, 7 января 2015. Триггер - это запоминающее устройство, хранящее одно из двух состояний - либо 0 либо 1. Первым будет рассмотрен RS-триггер. Его условное обозначение приведено на рисунке 1. S (SET) - вход установки значения 1. R (RESET) - вход сброса (установки значения 0). Входы прямые - активны при подачи логической единицы, неактивны при подаче логического нуля. Логика работы RS-триггера: RS - триггер с инверсными входами (рис. 2) работает аналогично, только входы становятся активны при подаче логического нуля, а неактивны при подаче единицы. Классической является реализация RS-триггера на элементах "ИЛИ-НЕ" (рис 3.): Таблица истинности: Когда оба входа активны, то Q=Q¯=0{\displaystyle Q={\overline {Q}}=0}. Но, по определению, они противоположны ⇒R=S=1⇒{\displaystyle \Rightarrow R=S=1\Rightarrow } запрещенное состояние, но оно однозначно определено. Эта особенность используется для ускорения переключения схемы. Будем считать, что в триггере записано значение "0", попробуем записать "1" (рис. 4). Если объединить входы R и S триггера, то выход будет определяться тем, какой из элементов сработает раньше ("генератор случайных чисел"). Схема и временные диаграммы такого подключения приведены на рисунке 5. Также RS-триггер можно реализовать на базе элеметов "И-НЕ" (рис. 6). Входы у такой реализации - инверсные. Добавляется вход синхронизации С (основное отличие от асинхронных триггеров, описанных выше). Логика работы - активный вход синхронизации разрешает работу триггера. При неактивном входе синхронизации триггер не реагирует на входные значения. То есть: Основное преимущество данного триггера - у него нет запрещенного состояния. Логика работы: Считается, что значения на выходе изменяются одновременно. Записать в триггер можно только изменяющееся значение, хранимое в триггере значение - нельзя. Если длительность управляющих сигналов больше времени переключения триггера - получаем автоколебательный режим (при наличии двух единиц на входах). При J=K=1{\displaystyle J=K=1\,\!} необходимо подать на вход сихронизирующий импульс, не превышая время переключения (время ПП) внутри JK-триггера. tJK=2tNOR+tAND{\displaystyle t_{JK}=2t_{NOR}+t_{AND}\,\!} Окончание автоколебательного процесса определяется длительностью сигнала синхронизации и времени установки триггера. Является синхронным триггером Таким образом триггер сохраняет значение поданное на вход D. При C=0{\displaystyle C=0} и R=S=1{\displaystyle R=S=1} возникает запрещенное состояние. Предназначен для хранения мнформации на входе D{\displaystyle D} при C=1{\displaystyle C=1} Триггер при подаче сигнала синхронизации меняет значение на выходе на противоположное. Может иметь вход стробирования Е (при Е=0 триггер не изменяет значение на выходе ни при какхи условиях). Если импульс синхронизации короткий (менее времени переключения триггера) то триггер работает в штатном режиме. При длительном импульсе синхронизации возможен автоколебательный режим. Может быть реализован и на синхронном RS-триггере (рис. 5.3). Короткие импульсы синхронизации (менее времени срабатывания триггера) не совсем удобны для управления триггерами. Как вариант модернизации существуют двухступенчатые триггеры. Они реагируют на смену значения на входе синхронизации (фронт:0-1, либо спад:1-0). В основе - RS триггер. Перезапись из первой во вторую ступень происходит при смене значения входа синхронизации. Запись происходит по спаду (изменение с 1 до 0). Основа - два обычных RS-триггера. Запись в первый триггер происходит при С=1 (второй триггер в это время в режиме хранения). При смене значения С на С=0 происходит запись значений из первого триггера во второй. Таким образом запись происходит по спаду сигнала синхронизации С (это обозначается наклонной чертой на входе синхронизации в обозначении триггера на схеме - см. рис 6.3). Логика работы та же что и у RS-триггера. С=1 - запись в первый триггер, С=0 - запись из первого во второй (запись по спаду). Поведение аналогично предыдущим триггерам кроме состояния J=1 K=1. Рассмотрим это состояние. При J=1K=1{\displaystyle J=1K=1} и C=1{\displaystyle C=1} вознмкает автоколебательный процесс: 0, 1, 0, 1 и т.д. JK-триггер должен переключаться в состояние, противоположное тому, в котором находится 2й триггер, т.е. используются только внутренние обратные связи (ОС). Для устранения этого недостатка можно модифицировать схему (рис. 6.6) Особенность схемы - наличие глубокой обратной связи (а именно, связи выходов второй ступени со входами первой ступени). В результате в триггер первой ступени записывыаются только значения. противоположные значениям на выходе, поэтому нет колебательного процесса (и генерации случайных чисел заодно). Двухступенчатые триггеры изменяют свои значения по спаду/фронту синхроимпульса, поэтому длительность импульсов не важна. Приведенные выше (рис. 6.5 и 6.6) схемы являются базовыми, теперь следует рассмотреть конкретные реализации. На входы D1 и D2 идет обратная связь с выходов D7, D8. Запись происходит при условии, что на выходах D1 и D2 одновременно присутствуют "1" (запись во вторую ступень). Запись в первую ступень происходит при противоположных значениях на выходах D7, D8. Запись в первую ступень происходит либо при C=1{\displaystyle C=1}, либо при J=K=0{\displaystyle J=K=0}. Перезапись - при C=0{\displaystyle C=0} (на выходах D1 и D2 - единицы). Еще эту схему можно получить на базе RS-триггеров (вывод схемы - на рис. 6.8) При необходимости в схему можно ввести асинхронные входы установки в 0 и 1 - они устанавливают схему независимо от схемы управления. Триггер сч такими входами называется универсальным (т.е. он имеет и синхронные. и асинхронные входы установки). Асинхронные входы нужны для инициализации. Пример - рис 7.1, вход Reset переустановка всех компонентов схемы в начальное состояние. В режиме хранения требуется реагирование на синхронные входы (на их значения). При режиме записи - приоритет у асинхронных входов. Имеет как синхронные, так и асинхронные входы установки. Конъюнкции D1 и D2 могут быть и 3хвходовыми, и 6-тивходовыми, а могут иметь и большую размерность, следовательнео, вместо одного сигнала J приходят несколько сигналов, объединенных конъюнкциями. Другими словами, на входе появляется "1", если на всех J - "1". Для входа K ситуация аналогичная. Классическая схема ступенчатого D-триггера представлена на рисунке 8.1. Состоит из трех асинхронных RS-триггеров (состоят из D1-D2, D3-D4, D5-D6 соответственно). Первую ступень образуют два триггера: (D1-D2) и (D3-D4), а вторая образуется, соответственно, на базе *D5-D6). T3{\displaystyle T_{3}\,} - с инверсными входами (рем хранение - оба значения равны "1"). Если C=0{\displaystyle C=0\,}, то T2=T3=1{\displaystyle T_{2}=T_{3}=1\,}, то есть при C=0T3=1{\displaystyle C=0T_{3}=1\,}, а при C=1{\displaystyle C=1\,} T3{\displaystyle T_{3}\,} определяется тем, что подается на вход D. При C=0,D=0{\displaystyle C=0,D=0\,} в T1{\displaystyle T_{1}\,} записывается некоторое значение, а T2{\displaystyle T_{2}\,} находится в запрещенном состоянии (две "1"). Если при C=1{\displaystyle C=1\,} T2=1{\displaystyle T_{2}=1\,} и T3=0{\displaystyle T_{3}=0\,}, то произойдет переход в режим записи и проихойдет запись "0" во вторую ступень. Рассмотрим случай, когда C=0,D=1{\displaystyle C=0,D=1\,}. Пусть D4=0{\displaystyle D4=0\,}, вход D4=0{\displaystyle D4=0\,}, тогда D1=1{\displaystyle D1=1\,}, можно наблюдать противоположную картину: T2{\displaystyle T_{2}\,} находится в режиме записи значения, а T1{\displaystyle T_{1}\,} - в запрещенном состоянии. При переключении C из "0" в "1" на D3 происходит то же изменение, что и на D2 - переход из 1 в 0. Тогда T3{\displaystyle T_{3}\,} находится в режиме записи логической единицы: При C=1{\displaystyle C=1\,} значение на входе D поменяется: 1→0{\displaystyle 1\rightarrow 0\,}, выход D4 установится в значение логической "1", поэтому D1{\displaystyle D1\,} станет равным 1 (его значение на выходе не меняется, на D2 - то же самое (только там - логический 0), поэтому значение на выходе D3 не меняется за счет D1 и D2). При C=1{\displaystyle C=1\,} значение на входе D изменяется в порядке 1→0→1{\displaystyle 1\rightarrow 0\rightarrow 1\,}, значение D3 меняться не будет. Следовательно, при C=0{\displaystyle C=0\,} на выходе значение не будет меняться, при C=1{\displaystyle C=1\,} значение навыходе тоже не меняется. Таким образом, запись производится при переключении с 0 на 1 (по фронту). В итоге, при C:0→1{\displaystyle C:0\rightarrow 1} происходит запись, то есть переключение в другое состояние (или в запрещенное состояние). Можно сделать из данного триггера универсальный (рис 8.3). Для этого необходимо добавить асинхронные входы во вторую и первую ступени (для того, чтобы не получать запрещенное состояние только при наличии (1)S¯{\displaystyle (1){\bar {S}}} и (1)R¯{\displaystyle (1){\bar {R}}} во второй ступени). Устанавливаем (1)S¯{\displaystyle (1){\bar {S}}} и (1)R¯{\displaystyle (1){\bar {R}}} на D1 и D4, чтобы не изменять выход в режиме хранения (при C=0{\displaystyle C=0\,} - на D2 и D3). Условное изображение полученного триггера приведено на рисунке 8.4. ru.bmstu.wiki Процессы, необходимые для функционирования любых технологических устройств ( в т. ч. и ПК) можно реализовать с помощью ограниченного набора логических элементов. Буфер, представляет из себя усилитель тока, служащий для согласования различных логических вентилей, в особенности имеющих в своей основе разную элементную базу (ттл или КМОП). Элемент, служащий для инвертирования поступающих сигналов - логическая еденица превращается в ноль, и наоборот. И - элемент логического умножения. Еденица (высокий уровень напряжения) на выходе, появляется только в случае присутствия едениц, на обоих входах, одновременно. Пример применения элемента И в реальном техническом устройстве:По тех. заданию, механический пресс должен срабатывать, только при одновременном нажатии двух кнопок, разнесенных на некоторое расстояние. Смысл тех. задания заключается в том, что бы обе руки оператора были заняты на момент хода пресса, что исключило бы возможность случайного травмирования конечности. Это может быть реализовано как раз, с помощью логического элемента И. И-НЕ - наиболее часто используемый элемент. Он состоит из логических вентилей И и НЕ, подключенных последовательно. Пример применения элемента И-НЕ в реальном техническом устройстве:По тех. заданию, ход стационарной транспортной платформы, управляемой электродвигателем, должен ограничиваться, нажатием путевых конечных выключателей - правого или левого. Как видите, применение электронных элементов логики для выполнения простейших схематических решений нецелесообразно. Более сложные, многоходовые операции - циклы, другое дело. Применение аппаратных(непрограммируемых) контроллеров на основе электронных логических элементов, в оборудовании довольно частое явление. ИЛИ - схема логического сложения. Логическая еденица на выходе, появляется в случае присутствия высокого уровня(еденицы) на любом из входов. ИЛИ - НЕ состоит из логических элементов ИЛИ и НЕ, подключеных последовательно. Соответственно, НЕ инвертирует значения на выходе ИЛИ. Этот вентиль выдает на выходе логическую еденицу, если на одном из входов - еденица, а на другом, ноль. Если на входах присутствуют одинаковые значения - на выходе ноль. Триггер Шмитта выдает импульс правильной формы, при сигнале произвольной формы на входе. Применяется для преобразования медленно меняющихся сигналов в импульсы, с четко очерчеными краями. На главную страницу elektrikaetoprosto.ru В радиоэлектронике существует множество механизмов и деталей, которые с помощью простейших операций позволяют создавать сложные машины. Правда, для такой цели их нужно очень много. И одним из важнейших механизмов подобного предназначения являются JK-триггеры. Они позволяют обеспечить машинную логику для выполнения простейших логических операций. Как это осуществляется? Как необходимо подключать JK-триггер? Как выглядит таблица истинности? На эти и другие вопросы можно будет найти ответы в рамках статьи. Триггерами называют целый класс электронных устройств, которые имеют такое свойство, как длительное нахождение в одном из двух устойчивых состояний. Чередование осуществляется под воздействием внешних сигналов. Текущее состояние триггера с легкостью распознаётся благодаря наличию выходного напряжения. Отличительной способностью всего класса является свойство запоминать двоичную информацию. Тут возникает вопрос: есть ли у триггеров память? В обычном понимании нет. Но, тем не менее, они остаются в одном из 2 состояний, причем и после прекращения подачи сигнала. Благодаря этой особенности и считается, что они могут запоминать двоичную информацию. При изготовлении триггеров на данный момент применяют полупроводниковые приборы (обычно полевые и биполярные транзисторы). Раньше использовали электронные лампы и электромагнитные реле. Своё применение триггеры нашли в интеграционных средах разработки, которые создаются для различных программируемых логических интегральных схем. Если говорить конкретнее, то их используют, чтобы организовать компоненты вычислительных систем: счетчики, регистры, процессоры и ОЗУ. Это триггер, который в случае получения на свои оба входа логической единицы меняет состояние своего выхода на противоположное значение. Одно из отличий от других подобных приборов – отсутствие запрещенных состояний, которые могут быть на основных входах. Как выглядит JK-триггер? Схема изображения может быть представлена с разной детализацией, а также зависимо от дополнений, которые были добавлены человеком. Как видите, в статье присутствуют различные изображения устройства. Также, используя базу JK-триггера, можно создать D- или Т-модель. Как вы сможете убедиться, просмотрев таблицу истинности, данный механизм в инверсное состояние переходит всегда, когда на оба входа осуществляется подача логической единицы. Различают два вида JK-триггеров: Также важным отличием данных моделей является то, что в них устранена неопределенность, которая может возникнуть в случае, если входные сигналы будут поданы в определённой комбинации. Также существенным преимуществом является тот факт, что они могут выполнять функционал T-, D- и RS-триггеров. Комбинированный тип имеет дополнительные асинхронные входы, которые используются для предварительной установки приборов в определённое состояние. Примитивный JK можно получить из RS, у которого есть динамическое управление. Для этого необходимо его дополнить обратными связями с выходов на входы. Для получения Т-триггера необходимо на входы подать уровень напряжения, который установит логическую единицу. В каких состояниях может быть главный герой статьи? Существует два принципа действий: асинхронный и синхронный. Во время первого происходит обмен данных независимо от входов. Синхронный JK-триггер действует одновременно, и из-за требований он является основным используемым элементом. Чтобы своими глазами увидеть, что и как работает, необходимо JK-триггер включить на макетной плате и собственноручно подавать различные входные сигналы. Это сродни обучению на гитаре – можно изучить десятки самоучителей, но пока не возьмете в руки гитару, вы никогда не научитесь. Так же и со схемами: без опыта разобраться во всём сложно. Для наблюдения можно подсоединить светодиодные индикаторы к инверсному и прямому выходу. При желании положение дел можно наблюдать и благодаря обычному вольтметру, но в связи с размерами данный вариант не очень удобный, если говорить о такой вещи, как JK-триггер. Что такое таблица истинности? Это специальный набор данных, который описывает логическую функцию. Что под ней понимают? В данном случае имеют в виду функцию, в которой значения параметров и её самой выражают логическую истинность. В качестве примера очень к месту будет вспомнить двузначную логику, где можно дать только два определения: ложь или истина. В качестве заменителей, когда говорят о компьютерных технологиях, часто вводят понятие 0 или 1. Причем использование данного инструментария оказалось удобным не только с позиции логики, но и при изображении в табличном варианте. Особенно часто их можно встретить в булевой алгебре или аналогичных системах логики. Но хватит информации, давайте посмотрим, как выглядит таблица JK-триггера. J K C Q(t) Q(t+1) Пояснения ноль х ноль ноль ноль Хранится информация ноль х ноль единица единица ноль ноль единица ноль ноль Хранится информация ноль ноль единица единица единица единица ноль единица ноль единица Установлена логическая единица, вход J равен единице единица ноль единица единица единица ноль единица единица ноль ноль Устанавливается логический нуль, при этом K равно единице ноль единица единица единица ноль единица единица единица ноль единица счетный режим триггера K=J=1 Как же сделан счетный режим? Для достижения цели используется перекрестная обратная связь. Благодаря такому механизму никогда не может создаться запрещённая комбинация. При этом особенность, что она перекрестная, вводит дополнительный режим работы – счетный. Так, когда на входы k и j подаются логические единицы одновременно, то JK-триггер переключается в счетный режим, подобно как и Т-модель. Сейчас можно сказать, что вам известны основы работы JK-триггеров. И их можно закрепить на практике. При работе всегда соблюдайте осторожность. Несмотря на то что на триггеры осуществляется подача низкого напряжения, которое обычно не превышает 14 Вольт, могут быть причинены дискомфортные ощущения и/или выйти из строя другая техника. Да и прочность самих приборов лучше не проверять, роняя их вследствие неаккуратности обращения. В целом, если понять смысл работы JK-триггеров, то можно также будет запросто разобраться и с другими представителями этого семейства. www.syl.ru В устройстве современной цифровой техники, триггер является одним из наиболее важных элементов, обеспечивающих ее работу. Он не играет роли базовой детали, поскольку его собственная логическая схема очень простая. Принцип работы триггера основан на его способности к запоминанию изменяющихся двоичных значений. На этом принципе было создано большое количество аналогичных устройств. Однако, в основе каждого такого прибора лежит конструкция простейшего RS-триггера. Благодаря RS-триггерам, стало возможным создание различных вычислительных устройств. Они одинаково используются в игровых приставках и в суперсовременных компьютерах. Эти приборы имеют входы установки и сброса, обозначаемые соответственно, как S и R. Кроме того, здесь имеются выходы – прямой и инверсный, обозначаемые символом Q. Чтобы их не перепутать, над знаком инверсного выхода ставится черточка. Любое из данных устройств является бистабильной системой, соблюдающей какое-либо устойчивое состояние в течение неограниченного времени. В некоторых случаях, отдельные модификации триггеров могут выполняться с применением элементов 2И – НЕ. Их отличие от базовой модели заключается в возможности перевода в другое состояние или активации путем потенциала, которым обладает логический нуль. При использовании других элементов, активация производится с помощью логической единицы. На практике, это выглядит следующим образом: когда на вход S подается положительный потенциал, то на прямом выходе образуется высокий потенциал, а на инверсном выходе – низкий. В результате, в ячейке памяти, которой является триггер, отложилась единица. При подаче высокого потенциала на вход R, устройство изменит свое состояние. После того, как питание включено, прибор принимает какое-либо одно устойчивое состояние. В этом и заключается основной принцип работы триггера. Перевести его в другое состояние можно только путем нажатия кнопки другого входа и подачи на него напряжения. Таким образом, устройство может поочередно переводиться из одного устойчивого состояния в другое. Чтобы преодолеть такой недостаток, как асинхронность, в сложных схемах подобных устройств осуществляется синхронизация с помощью тактовых импульсов, которые воздействуют на всю схему. Для выработки импульсов используется тактовый генератор. Установленное состояние триггера поддерживается сложной логической схемой, устанавливаемой на входе. Поэтому, прибор может изменить свое состояние только после формирования специального разрешительного сигнала. electric-220.ruПоследовательностные функциональные узлы. Триггеры. Схема триггера

Триггеры. Принцип работы | HomeElectronics

Внутреннее устройство триггера

Схема триггерной ячейки на логических элементах (RS триггер).

Схема триггерной ячейки на логических элементах (RS триггер). Входы Выходы R S Q -Q 0 0 Не определено 0 1 0 1 1 1 Без изменений 1 0 1 0 RS триггеры

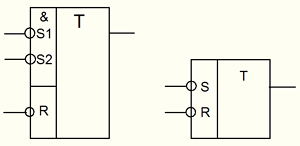

Обозначение RS триггера К555ТР2

Обозначение RS триггера К555ТР2 JK триггер

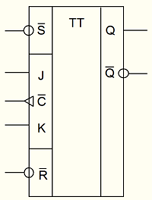

Обозначение JK триггера К555ТВ9.

Обозначение JK триггера К555ТВ9. Входы Выходы -S -R C J K Q -Q 0 1 Х Х Х 1 0 1 0 Х Х Х 0 1 0 0 Х Х Х Не определено 1 1 1→0 1 0 1 0 1 1 1→0 0 1 0 1 1 1 1→0 0 0 Не изменяется 1 1 1→0 1 1 Меняется напротивоположное 1 1 1 Х Х Не изменяется 1 1 0 Х Х Не изменяется 1 1 0→1 Х Х Не изменяется D триггер

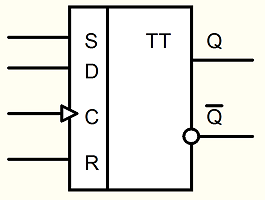

Обозначение D триггера микросхемы К555ТМ2

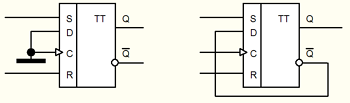

Обозначение D триггера микросхемы К555ТМ2 Входы Выходы -S -R C D Q -Q 0 1 X X 1 0 1 0 X X 0 1 0 0 X X Не определено 1 1 0→1 0 0 1 1 1 0→1 1 1 0 1 1 0 Х Не меняется 1 1 1 Х Не меняется 1 1 1→0 Х Не меняется  Схема замены D триггером: RS триггера (слева) и JK триггера в счётном режиме (справа).

Схема замены D триггером: RS триггера (слева) и JK триггера в счётном режиме (справа). 1. Схемы триггеров

НОУ ИНТУИТ | Лекция | Последовательностные функциональные узлы. Триггеры

RS-триггеры

(от англ. Reset - сброс) - вход сброса триггера в состояние логического нуля, S (от англ. Set - устанавливать) - вход установки триггера в логическую единицу,

(от англ. Reset - сброс) - вход сброса триггера в состояние логического нуля, S (от англ. Set - устанавливать) - вход установки триггера в логическую единицу,  - прямой выход триггера (состояние

- прямой выход триггера (состояние  считается для триггера единичным, а противоположное, при

считается для триггера единичным, а противоположное, при  , - нулевым),

, - нулевым),  - инверсный выход триггера.

- инверсный выход триггера. Рис. 7.1. RS-триггер в базисе ИЛИ-НЕ: а - функциональная схема; б - УГО

Рис. 7.1. RS-триггер в базисе ИЛИ-НЕ: а - функциональная схема; б - УГО ,

,  .

.  является для логического элемента ИЛИ-НЕ решающим сигналом, который переключит нижний элемент схемы на рис. 7.1,а в логический

является для логического элемента ИЛИ-НЕ решающим сигналом, который переключит нижний элемент схемы на рис. 7.1,а в логический  , поэтому

, поэтому  . Комбинация

. Комбинация  и

и  переключит верхний элемент ИЛИ-НЕ в 1:

переключит верхний элемент ИЛИ-НЕ в 1:  . Таким образом происходит установка триггера - его переключение в единичное состояние.

. Таким образом происходит установка триггера - его переключение в единичное состояние. ,

,  . Решающий для ИЛИ-НЕ сигнал

. Решающий для ИЛИ-НЕ сигнал  переключит выход

переключит выход  в нулевое состояние, а сочетание

в нулевое состояние, а сочетание  и

и  обеспечит переключение инверсного выхода в состояние

обеспечит переключение инверсного выхода в состояние  . Триггер сброшен - то есть пришел в устойчивое нулевое состояние.

. Триггер сброшен - то есть пришел в устойчивое нулевое состояние. , то состояние триггера будет определяться значениями

, то состояние триггера будет определяться значениями  и

и  , поскольку логический 0 не является решающим для элемента ИЛИ-НЕ. Допустим, ранее триггер был установлен: то есть

, поскольку логический 0 не является решающим для элемента ИЛИ-НЕ. Допустим, ранее триггер был установлен: то есть  и

и  . Тогда решающий сигнал

. Тогда решающий сигнал  будет через положительную обратную связь подан на нижний элемент ИЛИ-НЕ и состояние

будет через положительную обратную связь подан на нижний элемент ИЛИ-НЕ и состояние  будет подтверждено. На входы верхнего элемента ИЛИ-НЕ будет подано сочетание сигналов

будет подтверждено. На входы верхнего элемента ИЛИ-НЕ будет подано сочетание сигналов  и

и  , поэтому состояние прямого выхода триггера

, поэтому состояние прямого выхода триггера  будет подтверждено. Если же триггер был сброшен, то есть было

будет подтверждено. Если же триггер был сброшен, то есть было  и

и  , тогда решающий сигнал

, тогда решающий сигнал  бу дет через положительную обратную связь подан на верхний элемент ИЛИ-НЕ и состояние

бу дет через положительную обратную связь подан на верхний элемент ИЛИ-НЕ и состояние  будет подтверждено. На входы нижнего элемента ИЛИ-НЕ будет подано сочетание сигналов

будет подтверждено. На входы нижнего элемента ИЛИ-НЕ будет подано сочетание сигналов  и

и  . Таким образом, триггер хранит ранее записанную информацию.

. Таким образом, триггер хранит ранее записанную информацию. ,

,  . На входы обоих логических элементов ИЛИ-НЕ поданы решающие сигналы логической единицы, поэтому на выходах обоих элементов будут логические нули, то есть

. На входы обоих логических элементов ИЛИ-НЕ поданы решающие сигналы логической единицы, поэтому на выходах обоих элементов будут логические нули, то есть  и

и  . Если теперь одновременно подать

. Если теперь одновременно подать  , то за счет положительных обратных связей на оба логических элемента будут поданы 0, поэтому на выходах ИЛИ-НЕ установятся две решающие логические единицы, которые будут стремиться перевести выход другого ИЛИ-НЕ в логический 0. Кто победит в этом "поединке", зависит от того, в каком из элементов ИЛИ-НЕ переходный процесс закончится раньше. Допустим, в верхнем элементе процесс завершится раньше, тогда

, то за счет положительных обратных связей на оба логических элемента будут поданы 0, поэтому на выходах ИЛИ-НЕ установятся две решающие логические единицы, которые будут стремиться перевести выход другого ИЛИ-НЕ в логический 0. Кто победит в этом "поединке", зависит от того, в каком из элементов ИЛИ-НЕ переходный процесс закончится раньше. Допустим, в верхнем элементе процесс завершится раньше, тогда  подается на вход нижнего элемента ИЛИ-НЕ и приводит к переключению

подается на вход нижнего элемента ИЛИ-НЕ и приводит к переключению  . Таким образом, происходит сброс три ггера. Если же процесс завершится раньше в нижнем элементе, тогда

. Таким образом, происходит сброс три ггера. Если же процесс завершится раньше в нижнем элементе, тогда  подается на вход верхнего элемента ИЛИ-НЕ и приводит к переключению

подается на вход верхнего элемента ИЛИ-НЕ и приводит к переключению  . Происходит установка триггера. Для пользователя ситуация оказывается непредсказуемой, поскольку определяется разбросом параметров транзисторов, на базе которых выполнены логические элементы, входящие в триггер. В этой связи комбинация

. Происходит установка триггера. Для пользователя ситуация оказывается непредсказуемой, поскольку определяется разбросом параметров транзисторов, на базе которых выполнены логические элементы, входящие в триггер. В этой связи комбинация  приводит к недопустимому неустойчивому состоянию триггера. Она может применяться только при строгой очередности снятия сигналов

приводит к недопустимому неустойчивому состоянию триггера. Она может применяться только при строгой очередности снятия сигналов  и

и  .

. (

(  и

и  ), либо в устойчивом состоянии логической

), либо в устойчивом состоянии логической  (

(  и

и  ). Поскольку решающим для элементов ИЛИ-НЕ является сигнал логической единицы, в УГО входные управляющие сигналы

). Поскольку решающим для элементов ИЛИ-НЕ является сигнал логической единицы, в УГО входные управляющие сигналы  и

и  являются прямыми.

являются прямыми. и

и  .

. Рис. 7.2. RS-триггер в базисе И-НЕ: а - функциональная схема; б - УГО

Рис. 7.2. RS-триггер в базисе И-НЕ: а - функциональная схема; б - УГОСинхронный RS-триггер

в схеме дешифратора (рис. 4.2 в "Функциональные узлы комбинаторной логики. Дешифраторы" ). На первый и второй логические элементы И-НЕ одновременно поступает синхросигнал

в схеме дешифратора (рис. 4.2 в "Функциональные узлы комбинаторной логики. Дешифраторы" ). На первый и второй логические элементы И-НЕ одновременно поступает синхросигнал  (рис. 7.3,а). При неактивном уровне

(рис. 7.3,а). При неактивном уровне  на выходах первого и второго логических элементов И-НЕ будет логическая

на выходах первого и второго логических элементов И-НЕ будет логическая  . Она не является решающей для функции И-НЕ, поэтому триггер на третьем и четвертом элементах будет хранить записанную ранее информацию. Таким образом, триггер не реагирует на изменения входных сигналов при

. Она не является решающей для функции И-НЕ, поэтому триггер на третьем и четвертом элементах будет хранить записанную ранее информацию. Таким образом, триггер не реагирует на изменения входных сигналов при  . Если же синхросигнал становится активным (

. Если же синхросигнал становится активным (  ), то схема пропускает все переключения входных сигналов

), то схема пропускает все переключения входных сигналов  и

и  (табл. 7.3). Поскольку входные ключи производят инверсию входных сигналов

(табл. 7.3). Поскольку входные ключи производят инверсию входных сигналов  и

и  , активным их уровнем будет логическая

, активным их уровнем будет логическая  (рис. 7.3,б).

(рис. 7.3,б). Рис. 7.3. Синхронный RS-триггер: а - функциональная схема; б - УГО

Рис. 7.3. Синхронный RS-триггер: а - функциональная схема; б - УГОТриггер — Национальная библиотека им. Н. Э. Баумана

RS - триггер

Классическая реализация RS-триггера

S R Q(t) Q(t+1) no Q(t+1) Описание 0 0 0 0 1 режим хранения нуля 0 0 1 1 0 режим хранения единицы 1 0 0 1 0 установка в состояние 1 1 0 1 1 0 режим хранения 1 0 1 0 0 1 режим хранения нуля 0 1 1 0 1 сброс в ноль 1 1 0 0 0 запрещено 1 1 1 0 0 запрещено Временные диаграммы RS-триггера

Другая реализация RS-триггера

Синхронный RS-триггер

Схема синхронного RS-триггера

Рис. 2.1. Схема реализации синхронного RS-триггера. Синхронный JK-триггер

Схема JK-триггера

Рис. 3.2. Схема JK-триггера и временные диаграммы его работы. Рис. 3.3. Временные диаграммы. Конкретная реализация синхронного JK-триггера

Рис. 3.4. Конкретная реализация JK-триггера и временные диаграммы его работы. Рис. 3.5. Временные диаграммы. D-триггер

Т-триггер

Рис. 5.1. Условное обозначение T-триггера. Двухступенчатые триггеры

Двухступенчатый синхронный RS-триггер

Рис. 6.2. Схема двухступенчатого синхронного RS-триггера. Двухступенчатый D-триггер

Рис. 6.4. Схема и условное обозначение двухступенчатого D-триггера. Двухступенчатый JK-триггер

Рис. 6.5. Схема двухступенчатого JK-триггера. Универсальные триггеры

Рис. 7.1. Пример универсального триггера. Универсальный JK-триггер

Рис. 7.2. Обозначение универсального JK-триггера. Ступенчатый D-триггер

Работа триггера, логические элементы.

Логические вентили(логические элементы).

Буфер.

Инвертор.

Логическая схема И.

Логическая схема И - НЕ.

Логическая схема ИЛИ.

Логическая схема ИЛИ - НЕ.

Логическая схема исключающее ИЛИ.

Триггер Шмитта(Шмидта).

схема, таблица истинности :: SYL.ru

Что такое триггер?

Что такое JK-триггер?

Возможности

Таблица истинности

Реализация счетного режима

Заключение

Принцип работы триггера

Как устроен триггер

Как действует триггер

интернет-магазин светодиодного освещения

Пн - Вс с 10:30 до 20:00

Санкт-Петербург, просп. Энгельса, 138, корп. 1, тк ''Стройдвор''

Поделиться с друзьями: