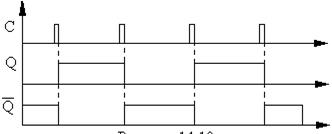

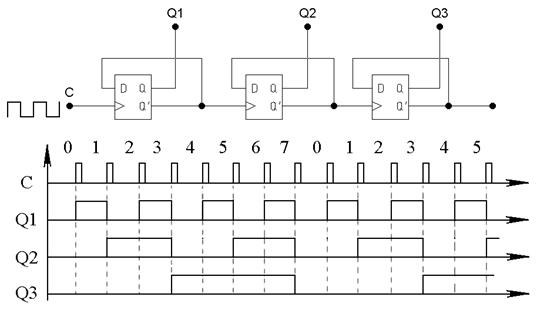

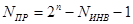

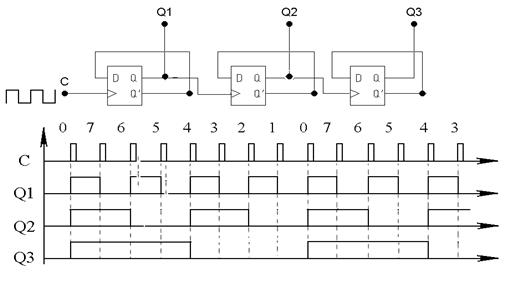

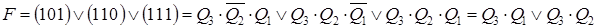

Т триггер довольно сложное устройство. Он изменяет свое состояние на противоположное после подачи каждого очередного импульса. Зачастую его используют в счетчиках, поэтому его иногда называют счетным триггером. Его схема сложнее чем схемы других триггеров и состоит из девяти логических элементов. Схема этого устройства с диаграммой работы приведена ниже: Как видно из схемы элементы Е6 и Е7 создают главный триггер (обозначенный на схеме как ГТ), а элементы Е1 и Е2 – дополнительный (обозначенный на схеме как ДТ). Как видим Т триггер имеет только один вход Т и имеет такой алгоритм работы: Пусть выходы основного и дополнительного триггеров имеют следующие состояния Важно отметить, что на изменение состояния ГТ влияет фронт тактового сигнала, а на состояние ДТ – спад этого сигнала. elenergi.ru 8. Т-триггер, JK-триггер, D-триггер по схеме MS с инвертором. Управление триггером по перепаду входного сигнала T – триггер. В соответствии с таблицей переходов логическое управление Т – триггера можно записать следующим образом: Уравнение (15.10) показывает, что Т-триггер выполняет операцию сложения по модулю 2 относительно переменных Tn и Qn, откуда и следует название триггера. Для переключения триггера в противоположное состояние необходимо на схему управления триггера подать информацию о текущем состоянии триггера. Для выполнения данной операции схему синхронного RS- триггера дополняют цепями обратной связи, причем выход Однако, наличие гонок делает схему, представленную на рис. 15.21 неработоспособной, если длительность сигнала на входе Т превышает время задержки переключения триггера Т – триггер с внутренней задержкой. Рассмотренные ранее семы асинхронных и синхронных RS– и D - триггеров переключаются по приходу определенного уровня напряжения на входы схем и называются схемами триггеров, переключаемых уровнем напряжения. Т – триггер с внутренней задержкой переключается по приходу на вход Т перепада с единичного уровня на нулевой. Варианты обозначений Т – триггера, переключаемого перепадом с единицы на ноль, показаны на рис. 15.26, перепадом с нуля на единицу – на рис. 15.27. В схеме Т - триггера устранены проскоки и обеспечивается однозначное переключение триггера при любой длительности сигнала на входе Т. Существенным достоинством триггера с внутренней задержкой является то, что большую часть времени БЯ блокирована. Воздействие помех на БЯ возможно только в течение времени задержки переключения элементов И-НЕ Минимальная длительность сигнала на входе Т определяется требованием установления нового кода на выходах элементов DD3 и DD4 и равна: Время переключения триггера Время восстановления триггера после перепада на входе Т с единицы на ноль определяется временем установления кода DD3 = «1», DD4= «1» на выходах элементов И-НЕ: Т С JK-триггер называют универсальным триггером. Его достоинство состоит в наличии развитой логике на входе. Однако большое количество внешних выводов ограничивает количество JK- триггеров, входящих в состав одной ИС. Обозначение JK- триггера на функциональных схемах показано на рис. 15.29б Триггеры, управляемые перепадом В триггерах, управляемых перепадом, используют одну последовательность тактовых импульсов, но новое состояние триггера устанавливается только после окончания действия тактирующего импульса. В отличие от триггеров с внутренней задержкой в триггерах, управляемых перепадом, для устранения гонок используются дополнительные бистабильные ячейки. Не рассматривая всех вариантов исполнения таких триггеров, остановимся подробнее только на схеме MS с инвертором и схеме трех триггеров. Более подробно варианты схем триггеров представлены в книге … Триггер, управляемый перепадом, по схеме MS с инвертором. В Пусть в исходном состоянии оба триггера Mи S записан нуль, так что Q’ = «0», В момент времени t1 на входе Т переходит на уровень логической единицы , сигнал на выходе DD5 - на уровень логического нуля. Логический ноль на выходе элемента DD5 обеспечит получение логической единицы на выходах элементов DD6 , DD7 . БЯ на элементах DD8 , DD9 переходит в режим хранения. Состояние ее выходов Q и В момент времени t2 состояние входа Т переходит с уровня логической единицы на уровень логического нуля, на выходе инвертора DD5 - с уровня логического нуля на уровень логической единицы. На выходах элементов DD1 , DD2 код снова равен DD1 = «1», DD2 = «1». БЯ на элементах DD3 и DD4 переходит в режим хранения. Ее состояние остается неизменным до прихода следующего импульса на счетный вход Т . Единичный сигнал на выходе DD5 и единица на выходе элемента DD3 переводит сигнал на выходе элемента DD6 на уровень нуля. Ноль на выходе элемента DD4 удерживает сигнал на выходе элемента DD7 на уровне логической единицы. Уровни сигналов на выходе БЯ DD8 , DD9 принимает значение, соответствующее единичному состоянию триггера. Далее процесс переключения триггера проходит подобным образом. Из временной диаграммы рис. 15.37 следует, что сигнал на выходе триггера M изменяется по приходу на входе Т с нуля на единицу. Сигнал на выходе триггера S изменяется по окончанию тактового импульса на входе Т единицы на ноль. Постоянство уровней на выходах Q и Импульсы на выходах всех элементов, кроме инвертора DD5 следует с частотой, в два раза меньшей частоты следования импульсов на входе Т. Сигнал на выходе элемента DD2 имеет импульсы, совпадающего по длительности с импульсом на входе Т. Сигнал на выходе элемента DD2 соответствует переходу счетного триггера из единичного состояния в нулевое, что видно из применения состояния выходов Q (выход DD8) и Триггер, управляемый переходом, выполненный по схеме MS не требует подбора времени задержки срабатывания отдельных компонентов схемы, как это имеет место в триггере с внутренней задержкой. Однако схема триггера, управляемого переходом по схеме MS с инвертором обладает низкой помехоустойчивостью. Низкая устойчивость объясняется теми же причинами, что и низкая помехоустойчивость синхронно RS триггера на элементах И – НЕ , когда помеха, поступившая на входы БЯ может применить их состояние и запомнится. Минимальная длительность сигнала на входе Т определяется требованием надежного установления нового хода на выходах триггера М и ранга. t4 =2t3сри-не (15.16) Время установления хода на выходах триггера после прихода перехода с единицы на ноль на вход С равно времени задержки срабатывания инвертора DD5 и время задержки срабатывания триггера S: t3тг=4t3ср и-не (15.17) Максимальная частота переключения триггера по схеме MS с инвертором (рис. 15.33): textarchive.ru На основе JK-триггеров и D-триггеров можно построить схемы, осуществляющие так называемый счетный режим. Такие схемы называют Т-триггерами или счетными триггерами, связывая с этим способ их функционирования. Рис.16 На рис. 16 представлены схемы организации Т-триггера на основе JK и D-триггеров. Счетный режим иллюстрируется временными диаграммами рис. 17. Рис. 17 В JK-триггере с входами установки логическим нулем счетный режим реализуется путем подачи констант J=K=1 и R=S=1 и входного сигнала Т на вход С. В соответствии с таблицей функционирования при каждом отрицательном перепаде входного сигнала Т состояние триггера изменяет свое значение на противоположное. В D-триггере счетный режим реализуется при помощи обратной связи (на вход D подается сигнал с инверсного выхода). Таким образом, всегда существует неравенство сигнала на входе D и сигнала на выходе Q: если Q=1, D=0. Следовательно, при каждом положительном перепаде сигнала на счетном входе С, в соответствии с принципом действия D-триггера состояние выхода будет изменяться на противоположное. Таким образом, на каждые два входных тактовых импульса Т-триггер формирует один период выходного сигнала Q. Следовательно, триггер осуществляет деление частоты где Счетчики Счетчик - устройство для подсчета числа входных импульсов. Число, представляемое состоянием его выходов по фронту каждого входного импульса, изменяется на единицу. Счетчик можно реализовать на нескольких JK или D триггерах, при этом триггеры должны работать в счетном режиме. В суммирующих счетчиках каждый входной импульс увеличивает число на его выходе на единицу, в вычитающих счетчиках каждый входной импульс уменьшает это число на единицу. Наиболее простые счетчики - двоичные. На рис. 18 представлен суммирующий двоичный счетчик и диаграмма его работы. Изменение направления счета. Как уже говорилось ранее, счетчики можно реализовать на триггерах. При этом триггеры соединяют последовательно. Выход каждого триггера непосредственно действует на тактовый вход следующего. Для того, чтобы реализовать суммирующий счетчик, необходимо счетный вход очередного триггера подключать к инверсному выходу предыдущего. Для того, чтобы изменить направление счета (реализовать вычитающий счетчик), можно предложить следующие способы: а) считывать выходные сигналы счетчика не с прямых, а с инверсных выходов триггеров. Рис.18 Число, образуемое состоянием инверсных выходов триггеров счетчика, связано с числом,образованным состоянием прямых выходов триггеров следующим соотношением: где n - разрядность выхода счетчика. В таблице 26 приведен пример связи числа на прямых выходах с числом на инверсных выходах триггеров счетчика. Таблица 26 б) изменить структуру связей в счетчике: подавать на счетный вход следующего триггера сигнал не с инверсного, а с прямого выхода предыдущего, как показано на рисунке 19. В этом случае изменяется последовательность переключения триггеров. Рис.19 Изменение коэффициента пересчета Счетчики характеризуются числом состояний в течение одного периода (цикла). Для схем на рис. 18 и 19 цикл содержит N = 23 = 8 состояний (от 000 до 111). Часто число состояний называют коэффициентом пересчета Ксч, который равен отношению числа импульсов Nc на входе к числу импульсов NQст на выходе старшего разряда за период: Ксч = Nc / NQст. Если на вход счетчика подавать периодическую последовательность импульсов с частотой fc, то частота fQ на выходе старшего разряда счетчика будет меньше в Ксч раз: Ксч =FC/FQ. Поэтому счетчики также называют делителями частоты, а величину Ксч - коэффициентом деления. Для увеличения величины Ксч приходится увеличивать число триггеров в цепочке. Каждый дополнительный триггер удваивает число состояний счетчика и число Ксч. Для уменьшения коэффициента Ксч можно в качестве выхода счетчика рассматривать выходы триггеров промежуточных каскадов. Например, для счетчика на трех триггерах Ксч = 8, если взять выход 2-го триггера, то Ксч = 4. При этом Ксч является целой степенью числа 2: 2, 4, 8, 16 и т. д. Можно реализовать счетчик, для которого Ксч - любое целое число. Например, для счетчика на трех триггерах можно сделать Ксч от 2 до 7, но при этом один или два триггера могут быть лишними. При использовании всех трех триггеров можно получить Ксч = 5...7: 22<Ксч<23. Счетчик с Ксч =5 должен иметь 5 состояний, которые в простейшем случае образуют последовательность: {0, 1, 2, 3, 4}. Циклическое повторение этой последовательности означает, что коэффициент деления счетчика равен 5. Для построения суммирующего счетчика с Ксч =5 надо, чтобы после формирования последнего числа из последовательности {0, 1, 2, 3, 4} счетчик переходил не к числу 5, а к числу 0. В двоичном коде это означает, что от числа 100 нужно перейти к числу 000, а не 101. Изменение естественного порядка счета возможно при введении дополнительных связей между триггерами счетчика. Можно воспользоваться следующим способом: как только счетчик попадает в нерабочее состояние (в данном случае 101), этот факт должен быть опознан и повлечь последующую выработку сигнала, который перевел бы счетчик в состояние 000. Рассмотрим этот способ более детально. Факт попадания счетчика в нерабочее состояние описывается логическим уравнением: Состояния 110 и 111 также являются нерабочими и поэтому учтены при составлении уравнения. Если на выходе эквивалентной логической схемы F = 0, значит, счетчик находится в одном из рабочих состояний: 0vlv2v3v4. Как только он попадает в одно из нерабочих состояний 5v6v7, формируется сигнал F = 1. Появление сигнала F = 1 должно переводить счетчик в начальное состояние 000, следовательно, этот сигнал нужно использовать для воздействия на установочные входы триггеров счетчика, которые осуществляли бы сброс счетчика в состояние Q1 = Q2 = Q3 = 0. При реализации счетчика на триггерах со входами установки логическим нулем для сброса триггеров требуется подать на входы сброса сигнал R=0. Для обнаружения факта попадания в нерабочее состояние используем схему, реализующую функцию F и выполненную на элементах И-НЕ. Для этого преобразуем выражение для функции: Соответствующая схемная реализация приведена на рисунок 20. Счетчик будет работать следующим образом: при счете от 0 до 4 все происходит как в обычном суммирующем счетчике с Ксч = 8. Установочные сигналы равны 1 и естественному порядку счета не препятствуют. Счет происходит по положительному фронту импульса на счетном входе С. В тот момент, когда счетчик находится в состоянии 4 (100), следующий тактовый импульс сначала переводит счетчик в состояние 5 (101), что немедленно (задолго до прихода следующего тактового импульса) приводит к формированию сигнала сброса, который поступает на установочные входы сброса триггеров. Рис. 20 В результате счетчик сбрасывается в 0 и ждет прихода следующего тактового импульса на счетный вход. Один цикл счета закончился, счетчик готов к началу следующего цикла. Применяя такие схемы с обратной связью для сброса счетчика, нужно иметь в виду, что операция сброса занимает конечное время, поэтому непосредственно перед сбросом счетчика в 0 на выходе первого триггера появляются кратковременные импульсы, или "иголки". Это не имеет значения при подключении счетчика напрямую к индикатору, но при использовании этого выхода счетчика в качестве источника тактовых импульсов могут возникнуть определенные проблемы. Схема, в которой это явление устранено, приведена на рис. 21. Важным отличием является то, что схема обнаруживает не факт попадания в нерабочее состояние 101, а факт попадания в состояние 100 и в следующем такте вырабатывает сигнал сброса. Рисунок 21 Синтез последовательностных устройств, страница 11. Схема т триггер

Т-триггер

=0, Q1=1, Q=1,

=0, Q1=1, Q=1, =0 (см. диаграмму работы выше). Пусть в определенный момент времени t1 на вход Т поступит импульс, то есть единичный сигнал. Тогда через инвертор Е5 на входы элементов Е3 и Е4 пойдет ноль, что вызовет появление единиц на входах

=0 (см. диаграмму работы выше). Пусть в определенный момент времени t1 на вход Т поступит импульс, то есть единичный сигнал. Тогда через инвертор Е5 на входы элементов Е3 и Е4 пойдет ноль, что вызовет появление единиц на входах  и

и  . Как мы можем видеть из таблицы истинности асинхронного R-S триггера сигналы

. Как мы можем видеть из таблицы истинности асинхронного R-S триггера сигналы  и Q не меняют свои значения. В то же время к элементам Е8 и Е9 от входа Т тоже подается тактовый импульс. К Е8 вдобавок еще и приходит сигнал ноль с Е2, а к Е9 с Е1 – единица. Поэтому ГТ поменяет сигнал Q1=0,

и Q не меняют свои значения. В то же время к элементам Е8 и Е9 от входа Т тоже подается тактовый импульс. К Е8 вдобавок еще и приходит сигнал ноль с Е2, а к Е9 с Е1 – единица. Поэтому ГТ поменяет сигнал Q1=0,  =1. Но далее эти изменения переданы не будут, так как на Е3 и Е4 действует значение ноль с инвертора Е5. Когда же импульс Т исчезает, то ГТ свое состояние не изменит, а ДТ изменит на обратный. Это обусловлено тем, что теперь на Е3 и Е4 приходит разрешающий импульс и под действием Q1=0,

=1. Но далее эти изменения переданы не будут, так как на Е3 и Е4 действует значение ноль с инвертора Е5. Когда же импульс Т исчезает, то ГТ свое состояние не изменит, а ДТ изменит на обратный. Это обусловлено тем, что теперь на Е3 и Е4 приходит разрешающий импульс и под действием Q1=0,  =1 эти значения появляются и на

=1 эти значения появляются и на  и Q. При подаче очередного сигнала на вход Т в момент времени t2, триггер таким же образом перейдет в противоположное состояние.

и Q. При подаче очередного сигнала на вход Т в момент времени t2, триггер таким же образом перейдет в противоположное состояние.8 т-триггер jk-триггер d-триггер по схеме ms с инвертором управление триггером по перепаду входного сигнала t – триггер

Триггером Т-типа (счетным триггером) называется логическое устройство с двумя устойчивыми состояниями и одним входом Т, изменяющее свое состояние на противоположное всякий раз, когда на Т вход поступает управляющий (счетный) сигнал. Таблица переходов счетного триггера показана на рис. 15.20.

Триггером Т-типа (счетным триггером) называется логическое устройство с двумя устойчивыми состояниями и одним входом Т, изменяющее свое состояние на противоположное всякий раз, когда на Т вход поступает управляющий (счетный) сигнал. Таблица переходов счетного триггера показана на рис. 15.20.

(15.10)

(15.10) соединяют со входом S, а вход Q – со входом R (рис. 15.21). Аналогично можно построить Т – триггер на основе D- триггера, если выход

соединяют со входом S, а вход Q – со входом R (рис. 15.21). Аналогично можно построить Т – триггер на основе D- триггера, если выход  соединить со входом D.

соединить со входом D.  .

.  Рассмотрим процесс возникновения гонок в схеме Т – триггера, показанной на рис.15.21. Пусть, триггер находится в нулевом состоянии, Q= «0»,

Рассмотрим процесс возникновения гонок в схеме Т – триггера, показанной на рис.15.21. Пусть, триггер находится в нулевом состоянии, Q= «0»,  = «1», и сигнал на ходе Т равен нулю (Т= «0»). На выходе элементов DD1, DD2 получим код DD1= «1» , DD2= «1» независимо от состояния выходов Q и

= «1», и сигнал на ходе Т равен нулю (Т= «0»). На выходе элементов DD1, DD2 получим код DD1= «1» , DD2= «1» независимо от состояния выходов Q и  . На БЯ, собранную на элементах DD3 , DD4 , подан код DD1= «1», DD2= «1». БЯ находится в режиме хранения. Состояния выходов Q и

. На БЯ, собранную на элементах DD3 , DD4 , подан код DD1= «1», DD2= «1». БЯ находится в режиме хранения. Состояния выходов Q и  не меняются пока Т= «0». Пусть сигнал на входе Т изменился и стал равным единице (Т= «1»). Пусть длительность этого сигнала превышает время задержки переключения

не меняются пока Т= «0». Пусть сигнал на входе Т изменился и стал равным единице (Т= «1»). Пусть длительность этого сигнала превышает время задержки переключения  . После того, как сигнал на входе Т стал равным единице, спустя время

. После того, как сигнал на входе Т стал равным единице, спустя время  , состояние выходов триггера Q и

, состояние выходов триггера Q и  изменится на противоположное и вновь будет подано на входы элементовDD1и DD2. Так как сигнал Т все еще равен единице, то изменение состояния выходов Q и

изменится на противоположное и вновь будет подано на входы элементовDD1и DD2. Так как сигнал Т все еще равен единице, то изменение состояния выходов Q и  вызовет повторное переключение триггера и т.д. Окончательное состояние триггера будет случайным и зависеть от соотношения времени установления триггера

вызовет повторное переключение триггера и т.д. Окончательное состояние триггера будет случайным и зависеть от соотношения времени установления триггера  и длительности сигнала на входе Т. Рассмотренный вид гонок называется «проскоками». Для устранения проскоков необходимо обеспечить постоянство сигналов на входах схемы управления, пока сигнал на входе Т равен единице (Т= «1»). Есть несколько способов решения проблемы проскоков. Один из этих способов состоит в установке задержки в цепи обратной связи (рис.15.22). Длительность задержки должна превышать длительность сигнала Т= «1» на входе Т.

и длительности сигнала на входе Т. Рассмотренный вид гонок называется «проскоками». Для устранения проскоков необходимо обеспечить постоянство сигналов на входах схемы управления, пока сигнал на входе Т равен единице (Т= «1»). Есть несколько способов решения проблемы проскоков. Один из этих способов состоит в установке задержки в цепи обратной связи (рис.15.22). Длительность задержки должна превышать длительность сигнала Т= «1» на входе Т.  Широкое распространение получила схема Т – триггера с внутренней задержкой, построенная на основе RS– триггера на элементах И-ИЛИ-НЕ (рис.15.23). Подадим на вход R этой схемы сигнал

Широкое распространение получила схема Т – триггера с внутренней задержкой, построенная на основе RS– триггера на элементах И-ИЛИ-НЕ (рис.15.23). Подадим на вход R этой схемы сигнал , на вход S – сигнал Q. Для удобства описания работы схемы покажем элементы «И» и «ИЛИ-НЕ» раздельно и перечертим схему RS – триггера в виде, показанном на рис.15.24. На этой схеме бывшие входы S и R обозначены как (S) и (R).

, на вход S – сигнал Q. Для удобства описания работы схемы покажем элементы «И» и «ИЛИ-НЕ» раздельно и перечертим схему RS – триггера в виде, показанном на рис.15.24. На этой схеме бывшие входы S и R обозначены как (S) и (R).  Рассмотрим работу этой схемы. При подаче на вход С логического нуля (С= «0») на выходах элементов DD11и DD22 также присутствуют логические нули (DD11= «0», DD22= «0»). Элементы «И» DD11и DD22 в этом режиме не определяют состояния выходов триггераQ и

Рассмотрим работу этой схемы. При подаче на вход С логического нуля (С= «0») на выходах элементов DD11и DD22 также присутствуют логические нули (DD11= «0», DD22= «0»). Элементы «И» DD11и DD22 в этом режиме не определяют состояния выходов триггераQ и  . БЯ образуется на элементах DD12, DD13,DD21, DD23 с управлением по асинхронным входам

. БЯ образуется на элементах DD12, DD13,DD21, DD23 с управлением по асинхронным входам  ,

,  . Поскольку выход Q соединен со входом (S), а выход

. Поскольку выход Q соединен со входом (S), а выход  - со входом (R), то при подаче на вход С логической единицы (С= «1») через элементы DD11и DD22 прежнее состояние БЯ подтверждается. Иначе говоря, до тех пор, пока сигнал на входе С равен логической единице, выходы Q и

- со входом (R), то при подаче на вход С логической единицы (С= «1») через элементы DD11и DD22 прежнее состояние БЯ подтверждается. Иначе говоря, до тех пор, пока сигнал на входе С равен логической единице, выходы Q и  сохраняют свое состояние. Состояние входов

сохраняют свое состояние. Состояние входов  ,

,  в этом режиме не влияет на состояние БЯ. Пусть, например, Q= «0»,

в этом режиме не влияет на состояние БЯ. Пусть, например, Q= «0»,  = «1», С= «1». Тогда в соответствии со схемой рис. 15.24 получим, что сигнал на выходе элементов DD21= «0», DD22 = «0», откуда следует, что сигнал на выходе

= «1», С= «1». Тогда в соответствии со схемой рис. 15.24 получим, что сигнал на выходе элементов DD21= «0», DD22 = «0», откуда следует, что сигнал на выходе  = «1». Этот сигнал поступает на вход элемента DD11, что при С= «1», дает на выходе элемента DD11 логическую единицу, и на выходе элемента DD13 подтверждает логический ноль (Q= «0»). Таким образом, БЯ триггера, показанного на рис. 15.24 при С= «1», блокирована. Управление БЯ возможно только при С= «0» и путем подачи соответствующих сигналов на входы

= «1». Этот сигнал поступает на вход элемента DD11, что при С= «1», дает на выходе элемента DD11 логическую единицу, и на выходе элемента DD13 подтверждает логический ноль (Q= «0»). Таким образом, БЯ триггера, показанного на рис. 15.24 при С= «1», блокирована. Управление БЯ возможно только при С= «0» и путем подачи соответствующих сигналов на входы  ,

,  .

. Окончательный вариант схемы Т – триггера с внутренней задержкой показан на рис.15.25. В этой схеме по сравнению со схемой RS - триггера рис. 15.24 добавлено два элемента «И-НЕ» DD3 и DD4, выходы которых подключены ко входам

Окончательный вариант схемы Т – триггера с внутренней задержкой показан на рис.15.25. В этой схеме по сравнению со схемой RS - триггера рис. 15.24 добавлено два элемента «И-НЕ» DD3 и DD4, выходы которых подключены ко входам  ,

,  предыдущей схемы. Кроме того, вход «С» обозначается как «Т», прежние

предыдущей схемы. Кроме того, вход «С» обозначается как «Т», прежние  ,

,  - как (

- как ( ), (

), ( ). При Т= «0», на выходах элементов DD3, DD4 получили логические единицы (DD3= «1», DD4= «1»). На прежние входы (

). При Т= «0», на выходах элементов DD3, DD4 получили логические единицы (DD3= «1», DD4= «1»). На прежние входы ( ), (

), ( ) поступаю две логические единицы одновременно, поскольку Т= «0», на выходах элементов «И» DD11и DD22 присутствуют логические нули. БЯ на элементах DD12, DD13, DD21, DD23 находится в режиме хранения. после подачи на вход Т логической единицы (Т= «1»), как было показано на примере схемы рис. 15.24, БЯ оказывается блокированной. Состояния выходов Q и

) поступаю две логические единицы одновременно, поскольку Т= «0», на выходах элементов «И» DD11и DD22 присутствуют логические нули. БЯ на элементах DD12, DD13, DD21, DD23 находится в режиме хранения. после подачи на вход Т логической единицы (Т= «1»), как было показано на примере схемы рис. 15.24, БЯ оказывается блокированной. Состояния выходов Q и  остаются неизменными в течение всего интервала времени, пока Т= «1». Постоянство значений Q и

остаются неизменными в течение всего интервала времени, пока Т= «1». Постоянство значений Q и  при Т= «1» является необходимым условием последующего однозначного переключения Т – триггера в необходимом направлении. На выходе элементаDD3 при Т= «1» получаем инверсное значение сигнала

при Т= «1» является необходимым условием последующего однозначного переключения Т – триггера в необходимом направлении. На выходе элементаDD3 при Т= «1» получаем инверсное значение сигнала  , на выходе DD4 - инверсное значение сигнала Q . Этот код подается на пока что блокированные входы (

, на выходе DD4 - инверсное значение сигнала Q . Этот код подается на пока что блокированные входы ( ), (

), ( )., что и обеспечит в последующем переход БЯ в состояние, противоположное предыдущему. Например, при нулевом состоянии БЯ, когда Q= «0»,

)., что и обеспечит в последующем переход БЯ в состояние, противоположное предыдущему. Например, при нулевом состоянии БЯ, когда Q= «0»,  = «1» и Т= «1» на входе (

= «1» и Т= «1» на входе ( ) будем иметь логический ноль (DD3 = (

) будем иметь логический ноль (DD3 = ( )= «0»), на входе (

)= «0»), на входе ( )- логическую единицу (DD4 = (

)- логическую единицу (DD4 = ( )= «

)= « 1»). Пусть, теперь, сигнал на входе Т переходит с логической единицы на ноль. Будучи подключенным ко входам элементов DD11и DD32 , ноль на входе Т сразу же заблокирует эти элементы. Тем самым разрешается переключение БЯ сигналами, снимаемыми с выходов элементов DD3 и DD4 , уровни сигналов на выходахDD3и DD4 остаются неизменными в течение времени задержки срабатывания

1»). Пусть, теперь, сигнал на входе Т переходит с логической единицы на ноль. Будучи подключенным ко входам элементов DD11и DD32 , ноль на входе Т сразу же заблокирует эти элементы. Тем самым разрешается переключение БЯ сигналами, снимаемыми с выходов элементов DD3 и DD4 , уровни сигналов на выходахDD3и DD4 остаются неизменными в течение времени задержки срабатывания  этих элементов. Сохраняющиеся на входах элементов DD3 и DD4 сигналы обеспечивают переключение БЯ в нужном направлении. Через

этих элементов. Сохраняющиеся на входах элементов DD3 и DD4 сигналы обеспечивают переключение БЯ в нужном направлении. Через  на выходах элементов DD3 и DD4 устанавливается код DD3 = «1», DD4= «1» и БЯ переходит в режим хранения. Для надежного переключения БЯ необходимо поддерживать сигналы на выходах элементов DD3 и DD4 неизменными в течение всего времени переключения БЯ. Поэтому схему триггера с внутренней задержкой необходимо проектировать так, чтобы выполнялось условие:

на выходах элементов DD3 и DD4 устанавливается код DD3 = «1», DD4= «1» и БЯ переходит в режим хранения. Для надежного переключения БЯ необходимо поддерживать сигналы на выходах элементов DD3 и DD4 неизменными в течение всего времени переключения БЯ. Поэтому схему триггера с внутренней задержкой необходимо проектировать так, чтобы выполнялось условие:  (15.11)

(15.11) . Недостаток схемы триггера с внутренней задержкой состоит в необходимости выдерживать соотношение (15.11) между временем задержки срабатывания элементов И-НЕ и ИЛИ-НЕ. Это требование накладывает определенные ограничения на параметры и топологию схемы триггера.

. Недостаток схемы триггера с внутренней задержкой состоит в необходимости выдерживать соотношение (15.11) между временем задержки срабатывания элементов И-НЕ и ИЛИ-НЕ. Это требование накладывает определенные ограничения на параметры и топологию схемы триггера. (15.12).

(15.12). после перехода сигнала на входе Т с единицы на ноль равно:

после перехода сигнала на входе Т с единицы на ноль равно: (15.13).

(15.13). (15.14).

(15.14).Триггеры JK-типа.

риггером JK-типа называется триггер, имеющий входы Jи K , который при J=K=1 выполняет инверсию предыдущего состояния триггера (т.е. реализуется Т-триггер)., а в остальных случаях JK- триггер работает как RS- триггер, при этом вход Jэквивалентен входу S, вход K эквивалентен входу R. Таблица переходов JK- триггера показана на рис. 15.28. Логическое уравнение JK- триггера имеет вид:

риггером JK-типа называется триггер, имеющий входы Jи K , который при J=K=1 выполняет инверсию предыдущего состояния триггера (т.е. реализуется Т-триггер)., а в остальных случаях JK- триггер работает как RS- триггер, при этом вход Jэквивалентен входу S, вход K эквивалентен входу R. Таблица переходов JK- триггера показана на рис. 15.28. Логическое уравнение JK- триггера имеет вид:  (15.15).

(15.15). хема JK- триггера может быть получена из схемы Т- триггера, если увеличить число входов схемы управления. Схема JK- триггера показана на рис. 15.29. Она получена из схемы Т – триггера с внутренней задержкой путем увеличения числа входов элементов «И-НЕ» DD3 , DD4. Обозначения элементов на схеме JK- триггера (рис. 15.29а) соответствует обозначениям элементов Т – триггера с внутренней задержкой (рис. 15.28), но на рис. 15.29 элементы «И» и «ИЛИ-НЕ» начерчены в виде единичного элемента «И-ИЛИ-НЕ».

хема JK- триггера может быть получена из схемы Т- триггера, если увеличить число входов схемы управления. Схема JK- триггера показана на рис. 15.29. Она получена из схемы Т – триггера с внутренней задержкой путем увеличения числа входов элементов «И-НЕ» DD3 , DD4. Обозначения элементов на схеме JK- триггера (рис. 15.29а) соответствует обозначениям элементов Т – триггера с внутренней задержкой (рис. 15.28), но на рис. 15.29 элементы «И» и «ИЛИ-НЕ» начерчены в виде единичного элемента «И-ИЛИ-НЕ». Схема RS-триггера , управляемого перепадом, по схеме MS с инвертором показана на рис. 15.33. В отличии от двухтактного триггера по схеме MS в данном типе триггера подается одна последовательность тактовых импульсов, причем на триггер S синхронизирующий сигнал поступает через инвертор. Триггер M собран на элементах DD1 … DD4 , триггер S – на элементах DD6…DD9.

Схема RS-триггера , управляемого перепадом, по схеме MS с инвертором показана на рис. 15.33. В отличии от двухтактного триггера по схеме MS в данном типе триггера подается одна последовательность тактовых импульсов, причем на триггер S синхронизирующий сигнал поступает через инвертор. Триггер M собран на элементах DD1 … DD4 , триггер S – на элементах DD6…DD9. Если на синхронизирующем входе присутствует уровень логического нуля (С= «0»), то запись новой информации в триггер M запрещена. При любом коде на входах Rи S на выходах элементов DD1 , DD2 имеем код DD1 = «1», DD2 = «1», и БЯ на элементах DD3 и DD4 находится в режиме хранения. На выходе инвертора DD5 получаем инвертированный сигнал

Если на синхронизирующем входе присутствует уровень логического нуля (С= «0»), то запись новой информации в триггер M запрещена. При любом коде на входах Rи S на выходах элементов DD1 , DD2 имеем код DD1 = «1», DD2 = «1», и БЯ на элементах DD3 и DD4 находится в режиме хранения. На выходе инвертора DD5 получаем инвертированный сигнал  = «1». Этот сигнал подается на синхронизирующие входы триггера S . Информация с выходов триггера M (Q’ и

= «1». Этот сигнал подается на синхронизирующие входы триггера S . Информация с выходов триггера M (Q’ и  ’) переписывается в триггер S . Оба триггера Mи S находится в одинаковом состоянии.

’) переписывается в триггер S . Оба триггера Mи S находится в одинаковом состоянии. При поступлении тактирующего сигнала на вход С (С= «1») информация с входов Rи S записывается в триггер M . Код на выходах Q’ и

При поступлении тактирующего сигнала на вход С (С= «1») информация с входов Rи S записывается в триггер M . Код на выходах Q’ и ’ соответствует новому состоянию триггера. На выходах инвертора DD5 имеем сигнал

’ соответствует новому состоянию триггера. На выходах инвертора DD5 имеем сигнал  = «0», запись в триггер S блокирована. Код на выходах Q и

= «0», запись в триггер S блокирована. Код на выходах Q и  триггера S сохраняется до тех пор, пока сигнал синхронизации С= «1» .

триггера S сохраняется до тех пор, пока сигнал синхронизации С= «1» .  После прихода сигнала синхронизации с уровня, соответствующего логической единице (С= «1»), на уровень логического нуля (С= «0») запись новой информации в триггер M вновь блокируется, и через инвертор DD5 разрешается перезапись информации с триггера M в триггер S. На выходах Q и

После прихода сигнала синхронизации с уровня, соответствующего логической единице (С= «1»), на уровень логического нуля (С= «0») запись новой информации в триггер M вновь блокируется, и через инвертор DD5 разрешается перезапись информации с триггера M в триггер S. На выходах Q и  устанавливается новое состояние, соответствующее коду, который присутствует на входах R и S перед поступлением на вход синхронизации С перепада с единицы на ноль. Обозначение RS – триггера, управляемого перепадом с единицы на ноль, показано на рис. 15.35. Так же, как и при обозначении двухтактного триггера, в обозначении триггера, управляемого перепадом, ставят буквы: «ТТ».

устанавливается новое состояние, соответствующее коду, который присутствует на входах R и S перед поступлением на вход синхронизации С перепада с единицы на ноль. Обозначение RS – триггера, управляемого перепадом с единицы на ноль, показано на рис. 15.35. Так же, как и при обозначении двухтактного триггера, в обозначении триггера, управляемого перепадом, ставят буквы: «ТТ». ходы

ходы  ,

,  , показанные на рис. 15.33, служат для асинхронной установки триггера в единичное или нулевое состояние в соответствии с таблицей переходов RS - триггера. Сигналы

, показанные на рис. 15.33, служат для асинхронной установки триггера в единичное или нулевое состояние в соответствии с таблицей переходов RS - триггера. Сигналы  ,

,  подают параллельно на БЯ триггеров Mи S , что обеспечивает одновременную асинхронную установку обоих триггеров в соответствующее состояние. При работе триггера по синхронным входам, асинхронные входы должны быть отключены. В схеме, показанной на рис. 15.33, это можно сделать, подав на входы

подают параллельно на БЯ триггеров Mи S , что обеспечивает одновременную асинхронную установку обоих триггеров в соответствующее состояние. При работе триггера по синхронным входам, асинхронные входы должны быть отключены. В схеме, показанной на рис. 15.33, это можно сделать, подав на входы  ,

,  логические единицы (

логические единицы ( = «1»,

= «1»,  = «1»). Обозначение RS – триггера, управляемого перепадом из единицы на ноль и имеющего дополнительные асинхронные входы, показано на рис. 15.36. Подобно триггерам с внутренней задержкой и многотактным триггерам триггеры, управляемые перепадом, используют для борьбы с гонками. Проиллюстрируем это положение на примере работы счетного триггера, управляемого перепадом, выполненного по схеме MS с инвертором. Счетный триггер можно построить на основе RS – триггера, показанного на рис. 15.33, если ввести обратные связи с выходов Q и

= «1»). Обозначение RS – триггера, управляемого перепадом из единицы на ноль и имеющего дополнительные асинхронные входы, показано на рис. 15.36. Подобно триггерам с внутренней задержкой и многотактным триггерам триггеры, управляемые перепадом, используют для борьбы с гонками. Проиллюстрируем это положение на примере работы счетного триггера, управляемого перепадом, выполненного по схеме MS с инвертором. Счетный триггер можно построить на основе RS – триггера, показанного на рис. 15.33, если ввести обратные связи с выходов Q и  на входы Rи S соответственно. Эти соединения показаны на рис. 15.33 пунктиром. Отметим, что Т- триггер имеет только один вход С сигнала синхронизации RS – триггера. Входы Rи S как внешние выводы не могут быть использованы, так как они задействованы под обратные связи. Отключим

на входы Rи S соответственно. Эти соединения показаны на рис. 15.33 пунктиром. Отметим, что Т- триггер имеет только один вход С сигнала синхронизации RS – триггера. Входы Rи S как внешние выводы не могут быть использованы, так как они задействованы под обратные связи. Отключим  ,

,  входы, для чего подадим нам них логические единицы. Полагая, что входы

входы, для чего подадим нам них логические единицы. Полагая, что входы  ,

,  отключены, в дальнейшем их рассматривать не будем.

отключены, в дальнейшем их рассматривать не будем. ’= «1», Q = «0»,

’= «1», Q = «0»,  = «1». Временные диаграммы работы триггера (рис. 15.33) в счетном режиме показана на рис. 15.37. На вход Т подаем последовательность синхроимпульсов. С выхода элемента DD5 снимаем инверсию этих импульсов. На выходах элементов DD3 (Q’ ) и DD8 (Q) имеем логические нули, на выходах элементов DD4 (

= «1». Временные диаграммы работы триггера (рис. 15.33) в счетном режиме показана на рис. 15.37. На вход Т подаем последовательность синхроимпульсов. С выхода элемента DD5 снимаем инверсию этих импульсов. На выходах элементов DD3 (Q’ ) и DD8 (Q) имеем логические нули, на выходах элементов DD4 ( ’) и DD9 (

’) и DD9 ( ) логические единицы. Логический нуль на входе Т установит на выходах логических элементов DD1 , DD2 логические единицы. Поскольку на выходе DD3 логический нуль, с выхода элемента DD6 снимем логическую единицу. На обоих входах элемента DD7 логические единицы, на выходе этого элемента присутствует логический ноль. Этот ноль подтверждает нулевое состояние БЯ на элементах DD8 , DD9 .

) логические единицы. Логический нуль на входе Т установит на выходах логических элементов DD1 , DD2 логические единицы. Поскольку на выходе DD3 логический нуль, с выхода элемента DD6 снимем логическую единицу. На обоих входах элемента DD7 логические единицы, на выходе этого элемента присутствует логический ноль. Этот ноль подтверждает нулевое состояние БЯ на элементах DD8 , DD9 . остается неизменным до тех пор, пока сигнал на входе Т= «1». Постоянство сигнала на выходах Q и

остается неизменным до тех пор, пока сигнал на входе Т= «1». Постоянство сигнала на выходах Q и  обеспечивает устойчивый переход триггера M в единичное состояние. При этом нуль на выходе DD8 сохраняет единицу на выходе DD2 , а две единицы на входах элемента DD1 переводит его выход в состояние нуля.

обеспечивает устойчивый переход триггера M в единичное состояние. При этом нуль на выходе DD8 сохраняет единицу на выходе DD2 , а две единицы на входах элемента DD1 переводит его выход в состояние нуля. в течение интервала, пока Т = & обеспечивает однозначность переключения триггера и отсутствие гонок.

в течение интервала, пока Т = & обеспечивает однозначность переключения триггера и отсутствие гонок. (выход DD9) триггера. Следовательно, импульсы на выходе элемента DD2 можно рассматривать как инвертированный сигнал переноса при добавлении к единичному состоянию триггера очередного счетного импульса. Аналогично, импульс на выходе элемента DD1 можно считать как инвертированный сигнал заема при вычитании из нулевого состояния триггера очередного счетного импульса, поступившего на вход Т.

(выход DD9) триггера. Следовательно, импульсы на выходе элемента DD2 можно рассматривать как инвертированный сигнал переноса при добавлении к единичному состоянию триггера очередного счетного импульса. Аналогично, импульс на выходе элемента DD1 можно считать как инвертированный сигнал заема при вычитании из нулевого состояния триггера очередного счетного импульса, поступившего на вход Т.  (15.17)

(15.17)Т-триггер (счетный триггер)

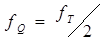

на ходе на 2:

на ходе на 2: ,

, — частота следования импульсов на выходе триггера.

— частота следования импульсов на выходе триггера.

Состояние прямых выходов

Число

Состояние инверсных выходов

Число

Q3

Q2

Q1

N

Q3’

Q2’

Q1’

N

.

. .

.

Похожие статьи:

poznayka.org

Синтез последовательностных устройств, страница 11

Заполним карту Карно:

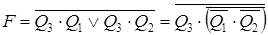

Т.о. функция переходов синхронного Т-триггера имеет следующий вид:

.

.

Если заменить в полученной формуле СТ=Т* и  , то получим функцию переходов асинхронного Т-триггера, т.е. если на вход асинхронного Т-триггера подать сигнал СТ, то получим синхронный Т-триггер.

, то получим функцию переходов асинхронного Т-триггера, т.е. если на вход асинхронного Т-триггера подать сигнал СТ, то получим синхронный Т-триггер.

Уравнение переходов синхронного JK-триггера, как известно, выглядит следующим образом:

.

.

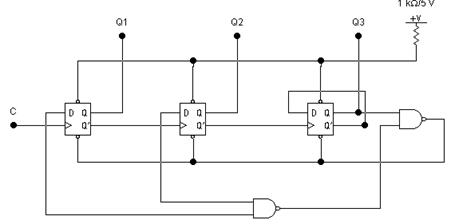

Если положить J=T и К=Т, то получим уравнение синхронного Т-триггера. Т.о. если в синхронном JK-триггере соединить вместе входы J и К, то получим синхронный Т-триггер. Кроме того, из синхронного JK-триггера можно легко получить и асинхронный Т-триггер, причем двумя способами.

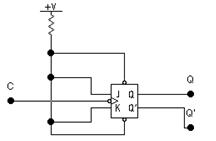

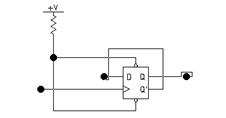

На следующем рисунке показаны использование синхронного JK-триггера в качестве синхронного Т-триггера, а так же способы получения асинхронного Т-триггера из синхронного JK-триггера:

На следующем рисунке показаны использование синхронного JK-триггера в качестве синхронного Т-триггера, а так же способы получения асинхронного Т-триггера из синхронного JK-триггера:

Кроме того, Т-триггер можно получить и из синхронного RS-триггера. Запишем функцию переходов синхронного RS-триггера:

.

.

Положим, что С=Т,  и R=Q и подставим данные замены в уравнение. Тогда:

и R=Q и подставим данные замены в уравнение. Тогда:

.

.

Полученное уравнение соответствует функции переходов асинхронного Т-триггера.

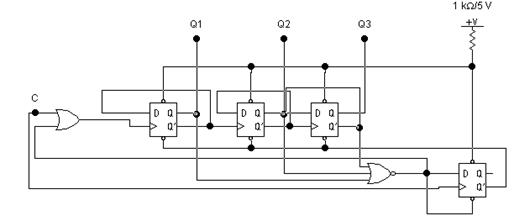

В соответствии с рассмотренными заменами, схема асинхронного Т-триггера, построенного на синхронном RS-триггере, выглядит следующим образом:

В соответствии с рассмотренными заменами, схема асинхронного Т-триггера, построенного на синхронном RS-триггере, выглядит следующим образом:

Временные диаграммы, отражающие работу асинхронного Т-триггера имеют следующий вид:

Если на вход Т подавать периодическую последовательность импульсов с периодом tвх, то на выходе получим меандр с периодом tвых=2tвх, т.е. Т-триггер может использоваться в режиме деления частоты.

Если на вход Т подавать периодическую последовательность импульсов с периодом tвх, то на выходе получим меандр с периодом tвых=2tвх, т.е. Т-триггер может использоваться в режиме деления частоты.

Временные диаграммы синхронного Т-триггера представлены на следующем рисунке:

Если на вход Т подать уровень логической единицы, то Т-триггер может быть использован, как делитель частоты синхроимпульсов. Это обстоятельство отражено на следующих временных диаграммах:

Двухступенчатый Т-триггер.

Двухступенчатый Т-триггер.

Асинхронный двухступенчатый Т-триггер может быть построен на основе двух синхронных RS-триггеров и одном инверторе согласно приведенной схеме:

Двухступенчатый синхронный Т-триггер строится по следующей схеме:

Синтез D-триггера.

Синтез D-триггера.

D-триггер называют триггер-защелка (от англ. Delay – задержка). Логика работы Dтриггера заключается в следующем: триггер D-типа устанавливает на выходе состояние, совпадающее с сигналом на входе D и удерживает это состояние до прихода следующего входного сигнала.

Таблица переходов асинхронного D-триггера выглядит следующим образом:

D | Q | Qt |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

vunivere.ru

Справочник "Цифровые Интегральные Микросхемы"

[ Содержание ]2.5.2. D-триггеры

D-триггером называется триггер с одним информационным входом, работающий так, что сигнал на выходе после переключения равен сигналу на входе D до переключения, т. е. Qn+1=Dn Основное назначение D-триггеров - задержка сигнала, поданного на вход D. Он имеет информационный вход D (вход данных) и вход синхронизации С. Вход синхронизации С может быть статическим (потенциальным) и динамическим. У триггеров со статическим входом С информация записывается в течение времени, при котором уровень сигнала C=1. В триггерах с динамическим входом С информация записывается только в течение перепада напряжения на входе С. Динамический вход изображают на схемах треугольником. Если вершина треугольника обращена в сторону микросхемы (прямой динамический вход), то триггер срабатывает по фронту входного импульса, если от нее (инверсный динамический вход) - по срезу импульса. В таком триггере информация на выходе может быть задержана на один такт по отношению к входной информации.

D-триггеры могут быть построены по различным схемам. На рис. 2.43,а показана схема одноступенчатого D-триггера на элементах И-НЕ и его условное обозначение. Триггер имеет прямые статические входы (управляющий сигнал - уровень логической единицы). На элементах DD1.1 и DD1.2 выполнена схема управления, а на элементах DD1.3 и DD1.4 асинхронный RS-триггер.

Рис. 2.43. Синхронный D-триггер: а - схема D-триггера на элементах И-НЕ и условное обозначение;б - временные диаграммы; в - преобразование синхронного RS-триггера в синхронный D-триггер;г - временные диаграммы записи и считывания.Если уровень сигнала на входе С = 0, состояние триггера устойчиво и не зависит от уровня сигнала на информационном входе D. При этом на входы асинхронного RS-триггера с инверсными входами (DD1.3 и DD1.4) поступают пассивные уровни /S = /R = 1.

При подаче на вход синхронизации уровня С = 1 информация на прямом выходе будет повторять информацию, подаваемую на вход D.

Следовательно, при C=0 Qn+1=Qn, а при C=l Qn+1=Dn. Временные диаграммы, поясняющие работу D-триггера, приведены на рис. 2.43,б.

D-триггер возможно получить из синхронного RS-триггера, если ввести дополнительный инвертор DD1.1 между входами S и R (рис. 2.43,в). В таком триггере состояние неопределенности для входов S и R исключается, так как инвертор DD1.1 формирует на входе R сигнал /S. Временные диаграммы записи в D-триггер напряжений высокого и низкого входных уровней и их считывание приведены на рис. 2.43,г. Обязательным условием правильной работы D-триггера является наличие защитного временного интервала после прихода импульса на вход D перед тактовым импульсом (вход С). Этот интервал времени tn+1-tn зависит от справочных данных на D-триггер.

Комбинированные D-триггеры имеют дополнительные входы асинхронной установки логических 0 и 1 - входы S и R. Схема и условное обозначение одного такого триггера представлены на рис. 2.44. Триггер собран на шести элементах И-НЕ по схеме трех RS-триггеров. Входы /S и /R служат для первоначальной установки триггера в определенное состояние.

Рис. 2.44. Комбинированный D-триггер и его условное обозначение.Если C=D=0, установить /S=0, а /R=1, то элементы DD1.1 ... DD1.5 будут закрыты, а элемент DD1.6 будет открыт, т. е. Q=l, /Q=0. При снятии нулевого сигнала со входа /S, откроется элемент DD1.1, состояние остальных элементов не изменится. При подаче единичного сигнала на вход С на всех входах элемента DD1.3 будут действовать единичные сигналы и он откроется, а элемент DD1.6 закроется: /Q = 1. Теперь на всех входах элемента DD1.5 действуют единичные сигналы и он будет открыт: Q = 0. Следовательно, после переключения триггера сигнал на выходе Q стал равным сигналу на входе D до переключения: Qn+1=Dn=0. После снятия единичного сигнала со входа С состояние триггера не изменится.

D-триггер с динамическим входом C может работать как T-триггер. Для этого необходимо вход С соединить с инверсным выходом триггера /Q (рис. 2.45,а). Если на входе D поставить дополнительный двухвходовый элемент И и инверсный выход триггера /Q соединить с одним из входов элемента И, а на второй вход подать сигнал EI, то получим T-триггер с дополнительным разрешением по входу (рис. 2.45,б).

Рис. 2.45. Схемы преобразования D-триггера. а - преобразование D-триггера в T-триггер и его временная диаграмма работы;б - преобразование D-триггера в в T-триггер с дополнительным входом расширения EI и его временная диаграмма работы;Микросхема ТМ2 содержит два независимых комбинированных D-триггера, имеющих общую цепь питания. У каждого триггера имеется один информационный вход D, вход синхронизации С и два дополнительных входа /S и /R независимой асинхронной установки триггера в единичное и нулевое состояния, а также комплементарные выходы Q и /Q (рис. 2.46). Логическая структура одного D-триггера (рис. 2.46) содержит следующие элементы: основной асинхронный RS-триггер (ТЗ), вспомогательный синхронный RS-триггер (Т1) записи логической единицы (высокого уровня) в основной триггер, вспомогательный синхронный RS-триггер (Т2) записи логического нуля (низкого уровня) в основной триггер. Входы /S и /R - асинхронные, потому что они работают (сбрасывают состояние триггера) независимо от сигнала на тактовом входе, активный уровень для них низкий (т. е. инверсные входы /S и /R).

Рис. 2.46. Структура D-триггера микросхемы ТМ2Асинхронная установка D-триггера в единичное или нулевое состояния осуществляется подачей взаимопротивоположных логических сигналов на входы /S и /R. В это время входы D и С не влияют.

Если на входы /S и /R одновременно подать сигнал низкого уровня (логический нуль), то на обоих выходах триггера Q и /Q будет высокий уровень (логическая единица). Однако после снятия этих сигналов со входов /S и /R состояние триггера будет неопределенным. Поэтому комбинация /S=/R=0 для этих входов является запрещенной.

Загрузить в триггер входные уровни В или Н (т. е. логические 1 или 0) можно, если на входы /S и /R подать напряжение высокого уровня: /S=/R=1. Сигнал от входа D передается на выходы триггера при поступлении положительного перепада импульса на вход С (изменение от низкого* к высокому). Однако, чтобы D-триггер переключался правильно (согласно таблице состояний, табл. 2.24), необходимо уровень на входе D зафиксировать заранее, т. е. до прихода перепада на вход С. Причем этот защитный временной интервал должен быть больше времени задержки распространения сигнала в триггере (определяется по справочнику).

| Асинхронная установка | 0 | 1 | X | X | 1 | 0 |

| Асинхронный сброс | 1 | 0 | Х | Х | 0 | 1 |

| неопределенность | 0 | 0 | Х | Х | 1 | 1 |

| Загрузка "1" (установка) | 1 | 1 | 1 | _/ | 1 | 0 |

| Загрузка "0" (сброс) | 1 | 1 | 0 | _/ | 0 | 1 |

Цоколевка микросхемы ТМ2 приведена на рис. 2.47, а основные параметры см. в табл. 2.20а.

Рис. 2.47. Условное обозначение и цоколевка микросхемы ТМ2Микросхемы ТM5 и ТМ7 содержат по четыре D-триггера, входы синхронизации которых попарно соединены и обозначены как входы разрешения загрузки EI. Если на такой вход разрешения EI подается напряжение высокого уровня, то информация, поступающая на входы D, передается на выходы триггеров. При напряжении низкого уровня на входе разрешения EI на выходах триггеров сохраняются предыдущие состояния (состояние входов D безразлично). В триггерах будет зафиксирована информация, имевшаяся на входах D, если состояние входа EI переключить от напряжения высокого уровня к низкому. Такие триггеры используются в качестве четырехразрядного регистра хранения информации с непарным тактированием разрядов, а также в качестве буферной памяти и элемента задержки. Каждый триггер микросхемы ТМ5 имеет только прямой выход Q, а каждый триггер микросхемы ТМ7 имеет прямые Q и инверсные /Q выходы. Функциональные схемы, цоколевка, схема одного D-триггера и временные диаграммы работы приведены на рис. 2.48, а, основные параметры триггеров даны в табл. 2.20, состояния триггеров даны в табл. 2.25.

Рис. 2.48. Функциональные схемы, цоколевки, структура D-триггера и временные диаграммы микросхем ТМ5, ТМ7.| Разрешение передачи данных на выход | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 | |

| Защелкивание данных | 0 | Х | Qn=1 | /Qn=0 |

Микросхемы. TM8 и ТМ9 содержат четыре и шесть D-триггеров соответственно. Они имеют общие входы синхронного сброса /R (установки в состояние низкого уровня) и входа синхронизации C. Структура ТМ8 и ТМ и их цоколевка приведены на рис. 2.49.

Рис. 2.48. Функциональные схемы и цоколевки микросхем ТМ8 и ТМ9.Триггеры микросхемы ТМ9 имеют только прямые входы Q, а триггеры ТМ8 - прямые и инверсные выходы Q и /Q. На входах C и /R поставлены дополнительные инверторы. Микросхемы К1533ТМ8, К1533ТМ9 имеют повышенную нагрузочную способность, т.е. на каждом из выходов поставлены дополнительные инверторы. Функционрированне триггеров в микросхемах ТМ8 и ТМ9 соответствует таблице состояний (табл. 2.26).

| Сброс | 0 | X | X | 0 | 1 |

| Загрузка "1" | 1 | 1 | _/ | 1 | 0 |

| Загрузка "0" | 1 | 0 | _/ | 0 | 1 |

Установка всех триггеров в состояние Q = 0 произойдет, когда на асинхронный вход /R подать напряжение низкого уровня - 0. Входы С и D в это время не действуют. Информацию от входов D можно загрузить в триггеры, если на вход /R подать напряжение высокого уровня - 1. Тогда при подаче на вход синхронизации С положительного перепада напряжения (фронта импульса) и предварительно поданного на вход D напряжения высокого или низкого уровня появится на выходе Q высокий или низкий уровень.

www.asvcorp.ru

Поделиться с друзьями: