RS-триггер представляет собой простейший управляющий автомат, реализованный обычно в виде цифровой электронной схемы, относящийся к классу последовательностных схем. Как известно, в цифровой схемотехнике к функциональным устройствам последовательностного типа относятся регистры, счетчики, генераторы чисел и управляющие автоматы, включая триггеры разных видов. В отличие от комбинационных логических схем, которые изменяют состояние в зависимости от фактических сигналов, поданных на их входы в определенное время, последовательностные логические имеют некоторую форму присущей им встроенной «памяти», так что они могут учитывать как предыдущее, так и фактическое состояние их входов и выходов. Общая структурная схема последовательностного устройства показана ниже. RS-триггер как цифровой управляющий автомат включает собственно память и комбинационную схему управления на типовых лигических элементах, реализующую его входной логический алгоритм. Если рассматривать эту схему применительно к простейшим схемам триггеров, то они не имеют структурно выделенной памяти в виде какой-то специализированной микросхемы или схемного узла. Память триггера существует на уровне функции, она словно встроена в алгоритм работы его комбинационной схемы управления. Проявлением этой «памяти» является так называемая бистабильность триггера, выходы которого могут находиться в одном из двух основных состояний: логической единицы (далее - 1) или логического нуля (далее - 0). Установившиеся значения своих выходов триггер запоминает («защелкивает» их) и сохраняет, пока не возникнет очередное изменение его входных сигналов. Если стандартные логические элементы являются строительными блоками комбинационных схем, бистабильные схемы, включая и RS-триггер, являются основными компонентами построения последовательностных логических устройств, таких, как регистры хранения данных, регистры сдвига, устройства памяти или счетчики. В любом случае рассматриваемые триггеры (разумеется, как и все последовательностные схемы) могут быть выполнены в виде следующих основных типов: 1. Асинхронный RS-триггер – схема, которая изменяет состояние сразу при изменении входных сигналов. Для рассматриваемого типа устройств ими являются сигналы на информационных входах R (сброс) и S (установка). Согласно установившейся практике, соответствующие входы называют так же, как и сигналы на них. 2. Синхронный RS-триггер, управляемый статически, работа которого синхронизирована с уровнем определенного тактового сигнала. 3. Триггер по п.2 с динамическим управлением, работа которого синхронизирована с моментами появления фронтов (или спадов) тактового сигнала. Таким образом, если изменения состояния выходов происходят только при наличии тактового сигнала, который подается на отдельный тактовый вход C, то триггер является синхронным. В противном случае схема считается асинхронной. Чтобы сохранить свое текущее состояние, последовательностные схемы используют обратную связь, т. е. передачу части выходного сигнала на ее вход. Простейший способ его сделать – соединить вместе пару двухвходовых логических элементов И-НЕ. При этом обратная связь с выхода одного элемента подается на вход другого (см. схему ниже). Как правило, в данной схеме входные сигналы показывают инверсными (с верхним подчеркиванием), хотя в дальнейшем при анализе работы используют обозначения прямых (неинвертированных) входов. Это сильно затрудняет понимание логики работы триггера. Поэтому мы не будем вводить инвертирование входов на этапе рассмотрения работы схемы на элементах И-НЕ, а учтем это в дальнейшем при ее модификации. Сколько входов и выходов имеет RS-триггер? Из схемы выше видно, что он содержит S-вход и R-вход, которые служат, соответственно, для установки и сброса схемы, а также прямой Q и инверсный Q̃ выходы. Но данный простейший триггер относится к виду асинхронных, его условное обозначение показано ниже. В синхронном устройстве имеется еще и вход C для тактовых импульсов. Рассмотрим, как происходит работа RS-триггера в этом состоянии, задаваемом значениями R = 0 и S = 1. Поскольку на вход R элемента И-НЕ Y подан уровень 0, то Q̃ =1 (логика И-НЕ). С выхода Y сигнал Q̃ также подан обратно на элемент X (вход "A"). Поскольку S = A = 1, то Q = 0. Если устанавливается R = 1, а вход S по-прежнему равен 1, то на входах Y имеем B = 0 и R = 1, а его выход Q̃ =1, т. е. он не изменился. Итак, если S = 1, то RS-схема триггера «защелкивается» в состоянии «Установлен» Q = 0 и Q̃ = 1, а смена сигнала R его не изменяет. В этом втором устойчивом состоянии Q̃ = 0, а Q = 1, и задается оно входами R = 1 и S = 0. Поскольку у элемента Х вход S = 0, то его выход Q =1 (логика И-НЕ). Сигнал Q подается обратно на элемент Y (вход "В"), и так как R = B = 1, то Q̃ = 0. Если S становится равен 1 при R = 1, то Q̃ остается равен лог 0, т. е. он не изменяется. Итак, при R =1 схема триггера снова «защелкивается» в состоянии «Сброшен» Q̃ = 0 и Q = 1, сохраняемом при любом сигнале S. Мы можем определить состояние сигналов Q и Q̃ по следующей таблице истинности: Видно, что когда S = R = 1, то Q и Q̃ могут быть равны как 1, так и 0 (но не одновременно!) в зависимости от уровней входов S или R перед возникновением данного состояния выходов. Таким образом, при условии S = R = 1 нельзя изменить состояние выходов Q и Q̃. Оно может измениться только при смене уровня с 1 на 0 на одном из входов. Значение S = R = 0 является нежелательным или недопустимым состоянием, и его следует избегать. Состояние S = R = 0 вызывает установку обоих выходов Q и Q̃ на уровне 1, в то время как состояние Q̃ всегда должно быть обратно Q. Результатом является то, что триггер теряет контроль над Q и Q̃, и если два входа теперь перейдут к состоянию 1, то схема становится неустойчивой и переключается в неопределенное состояние. Сказанное в предыдущем разделе иллюстрирует следующая диаграмма переключения. Как видно, при S = R = 0 возникает дисбаланс (неопределенность) состояния выходов. Он может привести к переключению одного из выходов быстрее, чем другого, в результате чего произойдет переключение триггера в то или иное состояние, которое может не совпадать с требуемым, и данные будут повреждены. Это неустойчивое состояние обычно называют мета-стабильным. Таким образом, подобный триггер-защелка может быть переведен в состояние «Установлен» путем подачи 0 на его S-ввод (при наличии 1 на R-вводе) и переведен в состояние «Сброшен» подачей 0 на R-ввод (при наличии 1 на S-вводе). Триггер входит в неопределенное состояние (мета-стабильное), если на оба его входа одновременно подается уровень 0. Переключение состояния выходов происходит с небольшой задержкой относительно изменения сигнала на одном из входов без использования тактового сигнала. Следовательно, рассмотренная выше схема представляет асинхронный RS-триггер. Как мы видели выше, базовые элементы И-НЕ рассмотренного RS-триггера работают так, что при его установке Q̃ = 1 и Q = 0, а при его сбросе Q̃ = 0 и Q = 1, хотя логичнее было бы в первом состоянии иметь Q = 1, а во втором - Q = 0. При этом еще и получается, что смена состояний происходит при падении уровня сигнала с 1 до 0. Таким образом, для правильной работы схемы триггера его входные сигналы нужно проинвертировать. Тогда переключения его состояний будут происходить при подаче положительных входных сигналов. Для этого в схему нужно добавить два дополнительных И-НЕ элемента, присоединенных как инверторы к S̃- и R̃-входам, как показано на рисунке ниже. Здесь на входах элементов И-НЕ уже представлены инверсные входные сигналы. Так же, как и с использованием И-НЕ элементов, можно построить простой RS-триггер с использованием двух ИЛИ-НЕ элементов, соединенных по такой же схеме. Она будет работать аналогичным образом, как и рассмотренная выше схема И-НЕ. При этом активным является высокий уровень сигналов на входах, а недопустимое состояние возникает, когда на оба входа подан уровень логической "1", как это показано в таблице истинности на рисунке ниже. Иногда желательно в последовательностных логических схемах иметь бистабильный триггер, изменяющий свое состояние, когда соблюдены определенные условия, независимо от состояния S- или R-входов. Такая схема может быть создана подключением двухвходного элемента И последовательно с каждого входом триггера. Объединив два входа элементов И, получим новый вход триггера. Добавление его означает, что выходы Q и Q̃ изменяют состояние, когда сигнал на нем является высоким, и, следовательно, он может быть использован в качестве тактового C-ввода, как показано на рисунке ниже. Когда сигнал на С-входе находится на уровне 0, то выходы двух элементов И - также на уровне 0 (логика элемента И), независимо от состояния двух входов S и R, а два выхода Q и Q̃ «защелкнуты» в последнем установившемся состоянии. Когда сигнал на С-входе изменяется на уровень 1, то схема отвечает как обычный бистабильный триггер, становясь прозрачной для установки и сброса состояний. Этот дополнительный C-вход также может быть подключен к выходу генератора тактовой частоты синхронизации, образуя тогда синхронный RS-триггер. Таким образом, данная схема работает как стандартная бистабильная триггерная «защелка», но выходы активируются только тогда, когда уровень 1 подан на C-вход, и отключаются при появлении уровня логического нуля. RS-триггер способен сохранять 1 бит цифровой информации. Если необходимо хранить несколько бит, например, цифровое двоичное слово из нескольких двоичных разрядов (в микроконтроллерах обычно 8 или 16), то триггеры могут соединяться параллельно, образуя регистры. Это простейшие устройства для временного хранения набора двоичных цифровых разрядов, в которых каждый триггер сохраняет значение одного разряда (0 или 1. т. е. один бит). Так, показанный ниже 4-разрядный регистр на RS-триггерах содержит четыре отдельных триггера. Любое двоичное число от (0000)2 до (1111)2 может быть сохранено в этом регистре просто путем установки или сброса соответствующего триггера. Давайте предположим, что первый триггер установлен (Q1 = 1), второй сброшен (Q2 = 0), третий также сброшен (Q3 = 0), а четвертый установлен (Q4 = 1). Тогда двоичное число, записанное в регистр, будет (1001)2. Кроме параллельных регистров, предназначенных для хранения цифровых слов, на RS-триггерах делаются и так называемые регистры сдвига, в которых разряды цифрового слова последовательно с приходом каждого тактового импульса сдвигаются влево или вправо на один разряд. Схема такого устройства на синхронных триггерах показана ниже. Подобные регистры находят применение в схемах последовательных интерфейсов, когда поступающие из управляющего контроллера цифровые слова побитно передаются в линию связи. www.syl.ru Всем доброго времени суток. В прошлой статье я рассказал об ограничителях сигнала, которые предназначены в первую очередь для ограничения импульса на определённом уровне напряжения. Сегодняшний мой пост о триггерах, которые также могут использоваться для формирования прямоугольных импульсов, но основное их назначение более сложное. В одной из предыдущих статей я рассматривал различные типы триггеров в интегральном исполнении, не вдаваясь во внутреннее устройство. Хочу напомнить, что же такое триггер. Триггер – это устройство, которое обладает двумя устойчивыми состояниями и способные под воздействием внешнего управляющего сигнала скачком переходить из одного устойчивого состояния в другое. Триггеры изготовляются в виде интегральных микросхем, но также могут быть выполнены на дискретных (отдельных) элементах. Триггеры на дискретных элементах применяются в нестандартной аппаратуре управления и контроля, и отраслях науки и техники, где используются повышенные уровни напряжения и тока. Симметричный триггер представляет собой двухкаскадный усилитель постоянного тока с положительной обратной связью, которая осуществляется через RC–цепи с коллектора одного транзистора на базу другого. Данная схема триггера имеет название симметричного триггера с независимым смещением. В данной схеме параметры левой и правой части идентичны, то есть Rb1 = Rb2, Rk1 = Rk2, R1 = R2, C1 = C2, транзисторы VT1 и VT2 имеют одинаковые параметры. Хотя триггер и называется симметричным, в реальных схемах никогда не удаётся допиться идентичности параметров транзистора, поэтому при подключении триггера к источнику питания один из его транзисторов окажется открытым (состояние насыщения), а другой транзистор будет в закрытом состоянии (состояние отсечки). В данном состоянии триггер может находиться сколько угодно долго (пока присутствует напряжение питания). Допустим, что после подключения триггера к источнику питания транзистор VT1 оказался в открытом состоянии, а транзистор VT2 – в закрытом состоянии. В этом случае коллекторное напряжение транзистора VT1 окажется примерно равным 0, а коллекторное напряжение VT2 – напряжению источника питания + Е. Казалось бы, за счёт резистора R1 транзистор VT2 должен был бы открыться, но так как на базу VT2 поступает дополнительное напряжение смещения Eb, поэтому на базе VT2 поддерживается напряжение меньшее, чем необходимо для открытия данного транзистора. Таким образом за счёт дополнительного источника смещения Eb схема триггера находится в устойчивом состоянии, а на выходах триггера поддерживаются парафазные напряжения. Для того чтобы на выходах симметричного триггера изменились напряжения необходимо подать на триггер внешний управляющий (запускающий) импульс напряжения или тока. В этом случае триггер переходит из одного устойчивого состояния в другое, транзисторы в схеме изменяют своё состояние: открытый транзистор – закрывается, а закрытый – открывается. В это же время на выходах триггера формируется перепад напряжения. Как говорилось выше для переключения триггера из одного устойчивого состояния в другое необходимо подать на его входы управляющий (запускающий) импульс. В зависимости от того как подавать управляющий импульс существует несколько видов схем запуска триггера: Для запуска триггеров используют короткие импульсы, которые формируются дифференциальными RC- или RL- цепочками. Так как при прохождении импульса через дифференциальную цепочку формируется два разно полярных импульса, то для предотвращения двойного срабатывания триггера между дифференциальной цепочкой и точкой входа запускающего импульса ставят диод, который отсекает второй импульс. В общем случае схема запуска имеет следующий вид: Рассмотрим схему раздельного запуска триггера с подачей управляющих импульсов в базовые цепи транзисторов. В данной схеме импульс, поданный на один из входов триггера, переключает его из одного устойчивого состояния в другое. Если импульс подать на другой вход, то состояние триггера изменится на противоположное. Схема запуска состоит из резисторов Rз1 и Rз2, конденсаторов Сз1 и Сз2, диодов VD1 и VD2. Остальные элементы являются цепями питания и смещения транзисторов VT1 и VT2. Симметричный триггер с раздельным запуском называется RS-триггером, он имеет два входа и два выхода. Входы, на которые подают управляющие импульсы, называются установочными и обозначают R и S, выходы триггера обозначают Q и –Q. Рассмотрим схему со счётным (общим) запуском триггера и подачей управляющих импульсов в базовые цепи транзисторов. В данном случае импульсы подаются на общий вход триггера, и каждый импульс приводит к изменению устойчивого состояния триггера. При рассмотрении работы данного типа триггера может возникнуть ощущение, что произойдёт двойное срабатывание, однако за счёт того что у открытого транзистора потенциал базы выше, чем у открытого, то один из диодов сработает раньше другого, а у открытого транзистора диод будет заперт высоким напряжением базы. Симметричный триггер с общим запуском называется T-триггером и частота переключения данного типа триггера вдвое меньше, чем частота поступающих импульсов запуска. На процесс перехода триггера из одного состояния в другое существенное значение оказывает время длительности управляющего импульса, например, если импульс имеет недостаточную длительность, то один из транзисторов триггера может не открыться и триггер не сработает. Кроме схем триггеров с внешним смешением существует ряд схем с автоматическим смещением, которое создается за счёт падения напряжения на сопротивлении Re в цепях эмиттеров транзисторов VT1 и VT2. Кроме резистора Re в цепи эмиттеров включается конденсатор Се, который выбирается достаточно большой ёмкости, чтобы за время переключения триггера из одного состояния в другое напряжение смещения практически не менялось. За счёт элементов Re и Се отпадает необходимость в отдельном источнике напряжения смещения, но это же приводит к тому что уменьшается уровень напряжения, которое может быть снято с выходов триггера. Кроме того на сопротивлении Re рассеивается достаточно большая мощность. В остальном же параметры схемы практически идентичны и схема с автоматическим смещением так же как схема с внешним смещением может использоваться как с раздельным запуском, так и с общим запуском. Теория это хорошо, но теория без практики - это просто сотрясание воздуха. Перейдя по ссылке всё это можно сделать своими руками Скажи спасибо автору нажми на кнопку социальной сети www.electronicsblog.ru Триггер представляет собой элементарный цифровой автомат. Он имеет два состояния устойчивости. Одному из них присваивается значение «1», а другому - «0». По способу реализации логических связей различают следующие виды упомянутых устройств: JK-триггер, RS-триггер, T-триггер, D-триггер и т. д. Предметом нашего сегодняшнего разговора являются автоматы типа JK. Они отличаются от RS-приборов тем, что при подаче на вход информации, запрещенной для RS-триггеров, инвертируют хранимые в них сведения. Представляем вашему вниманию таблицу переходов, которая описывает работу JK-триггера. При минимизации каты Карно выводится характеристическое уравнение для рассматриваемого устройства: Q(t+1)=K’t Qt V Jt Q’t. Из таблицы видно, что состояние прибора определяется не только значениями информации на входах J и K, но и состоянием на выходе Qt, которое ранее определяло JK-триггер. Это позволяет строить функциональные схемы таких устройств на двухступенчатых автоматах типа RS. JK-приборы бывают синхронными и асинхронными. Для проектирования JK-триггера из двухступенчатого устройства RS синхронного типа требуется соединить обратные связи выходов двухступенчатого автомата RS со входами логических элементов его первой ступени. Принцип работы JK-триггера: если на информационных (J и K) входах устройства подан уровень нуля, то на выходе элементов И-НЕ (1 и 2) устанавливается уровень единицы, и JK-триггер сохранит свое состояние. Например, Q будет равен логическому нулю, Q' - логической единице. В таком случае при подаче сигналов J и C, равных логической единице, на входе элемента И-НЕ1 устанавливается логический нуль и, соответственно, уровень логической единицы на входе первого T-триггера. При снятии синхронизирующего сигнала (С равен нулю) состояние упомянутого устройства Т-типа уровнем логического нуля с выхода И=НЕ3 передастся на вход второго T-триггера. В результате JK-триггер переключится в состояние логической единицы (в таком случае Q равен единице, а Q' равен нулю). Теперь, если на входе триггера (К и С) подается сигнал, равный логической единице, то на выходе элемента И-НЕ2 логический нуль установит первый Т-триггер в состояние нуля. После снятия синхронизирующего сигнала с выхода элемента И-НЕ4 логический нуль передастся на вход второго автомата типа Т, и JK-триггер переключается в состояние логического нуля. При проектировании сложных логических схем необходимы приборы разных типов. Поэтому выгоднее изготовить универсальный тип устройства, которое можно использовать в различных режимах работы и модификациях. В интегральной схемотехнике наибольшее распространение получили синхронные D- и JK-триггеры. В электронно-вычислительных машинах широко используют цифровые автоматы JK типа с групповыми J, K и дополнительными установочными R, S-входами. Каждая группа объединена конъюнкцией, что позволяет расширить логические возможности и JK-триггера. Автоматические устройства такого типа удобно использовать при конструировании счетчиков (узел ЭВМ, который осуществляет счет и хранение кода числа подсчитанных сигналов). Например, на фото показан счетчик на JK-триггерах. Структурная организация двоичных счетчиков с параллельным переносом значительно упрощается, если их строить на приборах типа JK со встроенными логическими элементами И. Также такие триггеры нашли применение при конструировании сдвигающих регистров. Регистры сдвига – это узлы, выполняющие смещение двоичной информации вправо и влево по регистру в зависимости от управляющих сигналов. fb.ru Триггер – простейшее устройство, представляющее собой цифровой автомат. Он имеет два состояния устойчивости. Одному из этих состояний присваивается значение «1», а другому - «0». Состояние триггера, а также значение двоичной информации, которая в нем хранится, определяется выходными сигналами: прямым и инверсным. В том случае, когда на прямом выходе установится потенциал, который соответствует логической единице, состояние триггера называется единичным (при этом потенциал на инверсном выходе равен нулю). Если же на прямом выходе нет потенциала, то состояние триггера называется нулевым. 1. По способу записываемой информации (асинхронные и синхронные). 2. По способу управлением информацией (статистические, динамические, одноступенчатые, многоступенчатые). 3. По способу реализации логических связей (JK-триггер, RS-триггеры, T-тригер, D-триггер и других типов). Основными параметрами всех типов триггеров являются наибольшее значение длительности входного сигнала, время задержки необходимого для переключения триггера, а также разрешающее время срабатывания. В этой статье поговорим о таком типе устройств, как RS-триггер. Они бывают двух типов: синхронные и асинхронные. Асинхронный RS-триггер конструктивно имеет два прямых (R и S) входа. Это устройство функционирует согласно таблице переходов. Запрещенной для такого триггера является комбинация сигналов на входах устройства, вызывающая состояние неопределенности. Эта комбинация может быть выражена требованием RtSt=0. При минимизации карты Карно выводится закон функционирования триггера, который называют характеристическим уравнением: Q(t+1)=St V R’tQt. При этом RtSt будет равно нулю. На функциональной схеме изображен RS-триггер асинхронного типа на элементах И-НЕ и во втором исполнении на элементах ИЛИ-НЕ. Второй тип – синхронный RS-триггер. Такое устройство конструктивно имеет три прямых входа S, R, и C. Отличие триггера синхронного типа от асинхронного заключается в наличии входа синхронизации (С). Он необходим по следующим причинам: ведь на входы устройства (логического элемента) сигналы поступают не всегда одновременно. Это связано с тем, что они проходят через различные типы и количество узлов, которые обладают разной задержкой. Это явление называют «состязанием». В результате таких «состязаний» полученные значения сигналов будут накладываться на предыдущие значения других сигналов. Все это приводит к ложному срабатыванию устройства. Это явление можно устранить подачей на вход устройства сигналов временного стробирования. А именно: на вход логического элемента, кроме непосредственно информационных сигналов, подаются ключевые синхронизирующие импульсы, к этому моменту информационные входные сигналы успеют зафиксироваться на входах. Главное условие правильности работы срабатывания логических каскадов в RS-триггере и управляемых ими логических схем – недопустимость одновременного действия сигнала Rt или St, переключающего устройство, и съема информации с выхода Q(t+1) триггера. В связи с этим в потенциальных сериях элементов содержатся только синхронные. RS-триггер синхронного типа представлен характеристическим уравнением: Q(t+1)=StCt V R’tQt V QtC't. На фото изображен RS-триггер синхронного типа на элементах И-НЕ. fb.ru Триггер (от английского “тrigger” ) – цифровое устройство, которое может иметь всего два (0 или 1) устойчивых состояния. При этом переход из одного состояния в другое осуществляется максимально быстро, временем переходным процессов на практике принято пренебрегать. Триггеры – это основной элемент для построения различных запоминающих устройств. Их можно использоваться для хранения информации, но объем их память чрезвычайно мал – триггер может хранить биты, отдельные коды или сигналы. Рис. 1. JK-триггер Триггеры способны сохранять свою память только при наличии питающего напряжения. Именно по этому их принято относить к оперативной памяти. Если выключить питающее напряжение и затем его снова включить, триггер переходит в случайное состояние – он может иметь на выходе как логический ноль, так и логическую единицу. Именно поэтому, проводя проектирование схем, надо обязательно предусмотреть вопрос приведения триггера в начальное («стартовое») состояние, исход из которого и проводится дальнейший расчет. В основу построения любого триггера положена схема, которая состоит из двух логических (И-НЕ или ИЛИ-НЕ), которые охватываются обратной положительной связью. В результате такого подключения схема может пребывать исключительно в одном (из двух возможных) устойчивых состояний. При этом в этом состоянии, если не приходят другие управляющие сигналы, схема может находиться по времени практически без ограничений – пока есть питающее напряжение. На рисунке ниже приводится пример подобной схемы – триггерной ячейки, созданной на основе 2 элементов И-НЕ Рис.2. Пример схемы триггерной ячейки Как видно, схема имеет 2 инверсных входа: сброс – обозначен на схеме R (сокращение от англ. Reset) и установка – обозначен S (сокращенно от Set), а так же два выхода: прямой, обозначенный Q и инверсный, обозначенный как – Q. Для правильной и стабильной работы триггерной ячейки должно соблюдаться одно правило – на ее входы не могут поступать одновременно отрицательные импульсы. Когда на вход –R поступает импульс при единичном сигнале на входе -S, выход переходит в состояние единицы (1), выход Q - нулевым. По обратной связи сигнал с Q (то есть 0) подается на второй вход в нижнем элементе. Поэтому и при прекращении поступления сигнала на входе – R (подан 0) состояние сигналов на выходах не изменяется – Q (0) и – Q (1). Итак, что подаче импульсов на вход –R состояние на выходе меняться не будет – схема находится в устойчивом состоянии. Такое же состояние система примет, если на – R подать 1, а на вход – S – 0. В этом случае на выходе Q будет единица, на - Q — нуль, и вне зависимости от подачи импульсов на входе – S система будет в устойчивом состоянии. Если на два входа одновременно подать сигналы, то в течении их действия на каждом выходе будет единичный сигнал. После прекращения подачи входных импульсов выходы произвольно перейдут в любое из двух устойчивых состояний. Аналогично, при включении тригерной ячейки, она случайным образом выберет одно из устойчивых положений. Таблица истинности для этой триггерной ячейки приведена ниже: Рис. 3 Число входов у триггера определяется его структурой и выполняемыми функциями. По тому, как информация записывается в триггер, они делятся на: В цифровой схемотехнике используют такие обозначения для входов триггера: S – раздельный вход, устанавливающий триггер в единичное состояние (на Q (прямом выходе) единица )R - раздельный вход, устанавливающий триггер в нулевое состояние (на Q (прямом выходе) ноль )С – вход синхронизации D – информационный вход (на этот вход подается информация для дальнейшего занесения её в триггер)Т - счетный вход Исходя из функционального назначения, триггеры классифицируют: Простейший тип триггеров, на основе которого в дальнейшем создаются другие типы. Он может быть построен как на логических элементах 2ИЛИ-НЕ (прямые входы) или 2И-НЕ (инверсные входы) Рис. 4. RS-триггер, схема построения и обозначение. А – на элементах ИЛИ-НЕ. Б – на элементах И-НЕ Самостоятельно, из-за очень низкой помехоустойчивости, в цифровой технике RS-триггеры практически не используются. Исключение – устранение влияния дребезжания контактов, возникающее при коммутации механических переключателей. В этом случае потребуется тумблер (кнопка), имеющий три вывода, при этом один из выводов подключается попеременно к двум остальным. Для получения RS-триггера используют D-триггер, у которого входы D и C замкнуты на «ноль». Принцип работы приведен на временной диаграмме: Рис.5. Схема устранения влияния дребезжания контактов Первым отрицательный сигнал, поступивший на вход –R переводит триггер в «0»-состояние, а первый отрицательный сигнал на на входе –S перебрасывает триггер в состояние единицы. Все остальные сигналы, которые вызваны дребезгом контактов, уже не смогут никак повлиять на триггер. При данной схеме подключения переключателя его верхнее положение будет соответствовать единице на выходе триггера, нижнее – нулю. Рис. 6. RS-триггер (микросхема 155ТМ2) RS-триггер – асинхронный, но возникают случаи, когда есть необходимость зафиксировать (сохранить) записанную информацию. Для этого используют синхронный (синхронизируемый) RS-триггер, который в этом случае состоит из двух частей: обычного RS-триггера и схемы управления. Рис.7. Синхронизируемый RS-триггер При такой схеме, пока на входе С=0, значение импульсов, поступающих на Х1 и Х2 не имеет значение, RS-триггер находится в режиме «хранение». При С=1 триггер активизируется и переходит в режим записи. Временная диаграмма представлена на рисунке ниже: Рис. 8 Подробнее о RS-триггере смотрите на видео: Триггер задержки, который используют для создания регистров сдвига и регистров хранения, неотъемлемая часть любого микропроцессора. Рис. 9. Схема D-тригера Имеет два входа – информационный и синхронизации. При состоянии С=0 тригер устойчив и при этом сигнал на выходе не зависит от сигналов, поступающих на информационный вход. При С=1 на прямом выходе информация будет точно повторять ту информацию, которая подается на вход D. На временной диаграмме приведен принцип работы D-триггера Рис.10. D-триггер. а) схематическое изображение б) временная диаграмма работы Таблица истинности D-триггера: Рис. 11 D-триггер, принцип работы и особенности применения рассмотрены на видео: По принципу работы JK-триггер практически полностью соответствует RS-триггеру, но при этом удалось избежать неопределенности, вызванной при одновременном поступлении на вход двух «единиц». Рис. 12. Графическое изображение JK-триггера Рис.13. JK-триггер на входе с логикой 3И В этом случае JK-триггер переходит в режим счетного триггера. На практике это приводит к тому, что при одновременном поступлении на вход «единичных» сигналов, триггер меняет свое состояние – на противоположное. Ниже приводится таблица истинности для JK-триггера: Рис.14 JK триггеры – очень универсальные устройства, при этом их универсальность носит двойной характер. С одной стороны, эти триггеры успешно используются для цифровых устройствах, так сказать, в чистом виде: в цифровых счетчиках, регистрах, делителях частоты и т.д. С другой стороны – очень легко из JK-триггера, соединив определенные выводы, получить любой необходимый тип триггера. Ниже приводится пример получения D – триггера из исходного JK – триггера, задействовав дополнительный инвертор Рис. 15. Схема получения D – триггера из исходного JK Особенности работы JK – триггера рассмотрены на видео: Другое название – счетные триггеры, на основе которых создают двоичные счетчики и делители частоты. Триггеры такого типа имеют только один вход. Принцип его работы – когда импульс поступает на вход тригерра, его состояние меняется на противоположное, при поступлении второго импульса – возвращается в исходное. Ниже приведена временная диаграмма работы Т-триггера Рис. 16. Временная диаграмма делителя частоты на основе Т-триггера Из неё становится понятно, почему Т-тригер называют делителем частоты. Переключение триггера происходит в момент, когда на вход поступает передний фронт синхроимпульса. В результате частота, с которой следуют импульсы на выходе триггера, оказывается в 2 раза меньше исходной – частоты синхроимпульсов, поступающих на вход. Если установка одного счетного триггера позволяет частоту импульсов разделить на два, то два последовательно подключенных триггера, соответственно, уменьшат эту частоту в 4 раза. Ниже приведен пример получения Т-тригерра из JK-триггера: Рис. 17. Т-тригер на основе JK-триггера Получив общее представление, что такое триггеры, рассмотрим некоторые примеры их практического использования. Один пример – устранение дребезга контактов с использованием RS-триггера рассмотрен выше. Одна из основных функций, для выполнения которых активно используются триггеры – формирование сигнала, у которого длительность соответствует длительности какого-либо выполняемого процесса (операции) в схеме. Выходной сигнал играет двойственную роль: Выходной сигнал триггера при этом может разрешать этот самый процесс, а может информировать остальные узлы устройства о том, что процесс идет (или, как говорят, служить флагом процесса). На схеме ниже приведен пример подобной работы Рис.18. Триггер в качестве флага процесса В момент прихода сигнала «Старт» происходит перебрасывание триггера в «единичное» состояние – операция (процесс) запущены. С приходом сигнала «Стоп» триггер переходит в «0»-состояние, процесс прекращается. Простейший вариант – это использование входов -S и –R, но при этом всегда остается вероятность возникновения ситуации неопределенности при одновременном приходе сигналов на оба входа. Чтобы избежать этого, на практике задействуют пары входов С и –S или –R и С. При использования пары входов –R и С надо подать на D единицу, при задействовании пары С и –S на вход D подается нуль. Универсальность и удобство такого решения еще и в том, что в роли сигналов «Стоп» и «Старт» может использоваться не только уровень сигнала, но и его фронт. Ещё одна область, в которой триггеры получили самое широкое распространение – синхронизация сигналов. Например, с помощью триггера очень просто избавляются от коротких паразитных импульсов, которые возникают на выходе комбинационной схемы, если несколько входных сигналов изменяются практически одновременно. Рис. 19. Схема синхронизации с помощью триггера В данном случае для синхронизации необходим синхропереход (синхросигнал), который сопровождает информационные входные сигналы (или входной код) и который задержан на время tз (его значение больше значения задержки для всей комбинационной схемы) относительно момента, когда началось изменение входных сигналов. Когда синхросигнал подается в триггере на вход С, а выходной сигнал этой комбинационной схемы – на вход D этого же триггера, то сигнал на выходе триггера (обозначен на графике Вых. 2) будет полностью свободен от наличия паразитных импульсов. При разработке цифровых схем, чья работа синхронизируются единым тактовым генератором, очень часто возникает проблема синхронизации работающей схемы и поступающего на неё внешнего сигнала. То есть необходимо обеспечить изменение этого внешнего (по отношению к тактовому сигналу в схеме - асинхронного) сигнала так, чтобы в результате менялся в соответствии с тактами задающего (тактового) генератора. Другими слова – этот сигнал из асинхронного должен стать синхронным для всей работающей схемы, в которую он поступает. Эта задача решается путем установки триггера. Самый простой вариант – внешний сигнал осуществляет разрешение/запрет на прохождения сигнала, генерируемого непрерывно работающим тактовым генератором. Самое простое решение, особенно если идет речь о RC-генераторе – просто отключать и запускать генератор в необходимое время. Но такая простота – кажущаяся. Прежде всего, нельзя включить генератор мгновенно – ему потребуется время для возбуждения, да и качество и форма генерируемого сигнала в начале будет отличаться от необходимого. Особенно ярко это проявляется с кварцевыми генераторами, останавливать и запускать которые не рекомендуется – после возобновления работы генератор возобновляет генерирование сигнала с задержкой, которая может равняться до 5 периодов тактовой частоты. При этом при каждом включении задержка будет разной. Кроме того, не всегда есть возможность прекращать работу тактового (задающего) генератора, особенно, когда от его работы напрямую зависит функционирование всей схемы. Поэтому для упрощения считают, что тактовый генератор функционирует непрерывно, а внешний управляющий сигнал будет отвечать за прохождение/блокирование сгенерированных импульсов. Рис. 20. Схема синхронизации сигнала разрешения Простейшее решение – организовать запрещение или пропускание импульсов, сгенерированных тактовым генератором, с использованием логического элемента 2И (на рис. вариант а). Но при этом велика вероятность того, что на выход системы будут проходить обрезанные (неполной длительности) импульсы, включая предельно короткие. Эти искаженные импульсы могут дестабилизировать работу системы в целом, внеся неопределенность в функционирование элементов. Синхронизирующий триггер (вариант б на рис. ) обеспечит на выходе пропускающего элемента 2И только «целые» импульсы, имеющие полную длительность. Проходящий через триггер разрешающий сигнал, тактирующийся разрешаемым сигналом, синхронизируется в результате с тактовым сигналом, что гарантирует появление на выходе исключительно целого числа тактовых импульсов и целого числа периодов, задаваемых тактовым генератором. Используя триггеры, можно создать линию задержки для цифровых сигналов. Для этого несколько триггеров (они обязательно должны тактироваться общим тактовым сигналом С) необходимо соединить в одну цепь последовательно. Такое включение позволит обрабатывать одновременно комбинационными схемами сразу несколько последовательных (по времени) состояний одного сигнала. Что такое триггеры и где они применяются рассмотрено на видео: 44kw.com Говоря об областях применения триггеров, целесообразно рассматривать D-триггеры, так как в большинстве случаев RS- и JK-триггеры могут быть заменены D-триггерами. Примеры такой замены показаны на Рис.3.18. RS-триггер получается из D-триггера, если в D-триггере не использовать входы C и D, например, соединить их с общим проводом (а). а). включение D-триггера для замены RS-триггера б). включение JK-триггера в счетном режиме Рис.3.18 Сложнее обстоит дело с заменой JK-триггера, в котором предусмотрено больше возможностей, чем в D-триггере. Однако обычно два информационных входа JK-триггера не так уж и нужны. А что касается счетного режима, в котором, пожалуй, наиболее часто работают JK-триггеры, то он легко реализуется на D-триггере в результате объединения информационного входа D с инверсным выходом (б). При этом по каждому положительному фронту сигнала С триггер будет менять свое состояние на противоположное: нуль на прямом выходе будет сменяться единицей и наоборот. То есть частота входного сигнала триггера будет меньше частоты входного тактового сигнала С в два раза. На Рис.3.19. представлены другие варианты схем позволяющие преобразовать один триггер в другой. а) триггер «мастер-помощник» D в роли триггера Т б) триггер «мастер-помощник» JK в роли триггера D в) JK триггер в роли триггера Т Рис.3.19 Особенности триггеров обусловливают наиболее широкий диапазон схем их включения для решения самых разных задач. С помощью триггера (любого типа) просто решается задача устранения влияния дребезга контактов механических переключателей (Рис. 3.19). В данном случае необходим тумблер (или кнопка) с тремя выводами, один из которых попеременно подключается к двум другим. При этом первый отрицательный импульс на входе –R перебрасывает триггер в состояние нуля, а первый отрицательный импульс на входе –S - в состояние единицы. Последующие же импульсы на обоих этих входах, вызванные дребезгом контактов, уже никак не влияют на триггер. Нижнее (Рис. 3.19 а) положение выключателя соответствует нулю на выходе триггера, а верхнее - единице. а) б) Рис. 3.19 Подавление дребезга контактов выключателя с помощью триггера Основное применение триггеры находят в тех случаях, когда надо сформировать сигнал, длительность которого соответствует длительности какой-то выполняемой операции, какого-то продолжительного процесса в схеме. Выходной сигнал триггера при этом может разрешать этот самый процесс, а может информировать остальные узлы устройства о том, что процесс идет (или, как говорят, служить флагом процесса). Например, в схеме на рис. 3.20в начале процесса (операции) по сигналу "Старт" триггер перебрасывается в единицу, а в конце процесса (операции) по сигналу "Стоп" - обратно в нуль. Рис. 3.20Использование триггера в качестве флага процесса Для сигналов "Старт" и "Стоп" можно, конечно, использовать входы триггера -R и -S. Однако более правильным и универсальным решением будет выбор пары входов С и -R или С и -S, что предотвратит неоднозначность поведения триггера при одновременном приходе сигналов "Старт" и "Стоп". Если используются входы С и -R, то на вход D надо подать единицу, а если применяются входы С и -S, то на вход D надо подать нуль. Такое решение удобно еще и тем, что в качестве одного из сигналов "Старт" и "Стоп" может выступать не уровень, а фронт. Именно этот фронт (в нужной полярности) и надо подать в этом случае на тактовый вход триггера С. studfiles.net При работе со схемами, которые должны монтироваться в различные электронные приборы или продукты любительской радиоинженерии, для решения поставленных задач и достижения целей нередко используется D-триггер. Но перед тем как использовать эту деталь, необходимо хорошо разобраться в специфике работы устройства. Приступим. Под этим названием понимают целый класс электронных устройств, которые обладают способностью на протяжении длительного времени находиться в одном из двух устойчивых состояний, а при подаче сигналов управления – менять его. D-триггер – это такая составляющая схем, которая позволяет организовывать задержки выполнения. Они имеют, как правило, два входа. Перед тем как приступать к рассказу о применении этого устройства, необходимо объяснить, как работает D-триггер. Принцип работы такой: когда приходит импульс синхронизации на вход С, то устройство начинает активно работать. Информация, полученная им, сохранится даже после прекращения подачи импульсов и десинхронизации сигнала, приходящего на порт С. Поскольку информация будет сохраняться до прихода ещё одного импульса, который всё поменяет, то второе название, полученное этим устройством – триггер с запоминанием информации. Организовать работу модели D можно с любых (теоретически) моделей JK или RS, если к ним подавать взаимно инверсные сигналы, причем подавать одновременно. Если опытный человек посмотрит на схему этого типа устройств, то он может заметить натренированным глазом, что она состоит из двух (как правило) усилительных каскадов. Выходы на каждом из них подключены ко входу остальных через резисторы. Подбираются они так, чтобы тот каскад, у которого открыт транзистор, уверенно запирал другой. Можно провести интересный эксперимент: при подаче напряжения на триггер внутри него каскады начнут «бороться» между собой, чтобы закрыть друг друга. Схематически это устройство можно узнать на схемах по таким особенностям: С помощью одного из входов (тактового) можно провести общую синхронизацию триггера относительно остальных элементов схемы. Импульс, который поступает на другой вход, меняет положение устройства, но только в том случае, если на тактовом входе была перед этим установлена логическая единица. Вот так описательно выглядит D-триггер. Схема, точнее, фотография схемы представлена в статье. В подзаголовке говорится о «триггерных системах» из-за того, что сами по себе эти устройства мало чего стоят. Но если необходимо сделать временную задержку перед выполнением или во время процедуры – их весьма сложно заменить. Также тот факт, что D-триггер может запросто длительное время работать без дополнительной настройки, позволяет его сделать очень ценным элементом любых схем, где необходима временная задержка. Для радиолюбителей они стали настоящим спасением при конструировании автоматических роботизированных станков, ведь эти элементы позволяют сделать временную задержку, необходимую для того, чтобы в рабочую область подать материал или деталь. Синхронные устройства имеют только логические (или по-другому – информационные) входы. Асинхронные механизмы срабатывают сразу, как только получили сигнал. Они не ждут, пока пройдёт временная задержка в тех элементах, которые образуют триггер. Асинхронный D-триггер не работает как устройство в обычном понимании. Благодаря этому он имеет один несомненный плюс: всегда, когда подаётся сигнал на вход, этот логический элемент сразу меняет значение выхода, а не ждёт определённой тактовой частоты. Для тех, кто умеет создавать близкие к идеальным схемы, триггеры будут весьма полезны. Синхронные имеют не только информационные входы, у них также есть отдельный вход для подачи тактового сигнала. И именно к ним относится D-триггер. Он состоит из комбинационных схем (КС) и элементов памяти (ЭП). Из-за того что при наличии тактового сигнала вся работа ориентируется на один такт, триггеры и разделили на синхронные и асинхронные устройства. Но конструктивная разница на этом не исчерпывается. Так, именно благодаря тактовому сигналу, его воздействию, можно полностью исключать из внимания переходные процессы, что позволяет, в свою очередь, облегчить работу с электроникой. Именно поэтому синхронный D-триггер является более популярным и используемым на практике. Даже пример, который был приведён в начале статьи, подразумевал его использование. Динамические устройства представляют собой систему, одно состояние которой (логическая единица) характеризуется наличием на выходе непрерывающейся последовательности импульсов, имеющих определённую частоту. При втором состоянии (логический ноль) отсутствуют выходные импульсы. Изменение состояний проводится с помощью подачи внешнего импульса. Динамический D-триггер из-за необходимости подачи энергии нашел довольно слабое распространение. Статистическими триггерами называют устройства, каждое состояние которых можно характеризовать неизменным уровнем выходного напряжения (можно в учебной литературе встретить фразу «выходными потенциалами»). Для высокого состояние оно будет близким к напряжению питания, для низкого будет сремиться к нулю. Благодаря такому способу представления выходных данных статистические триггеры часто называют потенциальными. Они делятся на две подгруппы, которые различаются по своему практическому значению для любителей электроники: Своим названием подгруппы обязаны способам организации электрических связей между составляющими элементами схемы. Так, в симметрических триггерах при рассмотрении схемы можно заметить симметрию расположения элементов. В несимметрических устройствах она не наблюдается. Основная задача, которая решается с помощью таких устройств - с их помощью создается счетчик на D-триггерах. Они отличаются стабильностью своей работы и эффективностью контроля временных функций. Применение D-триггер нашел в промышленном оборудовании, а также в самодельных автоматизированных комплексах, которые работают с применением временных задержек. Хотя могут они использоваться и в других случаях, такая практика не является распространенной, и существует исключительно в целях утоления любопытства конструкторов. Так, создавать регистр на D-триггерах не очень практично, но благодаря дешевизне устройства такая практика довольно распространена. www.syl.ruRS-триггер. Принцип работы, функциональные схемы, таблица переходов. Триггеры схемы включения

RS-триггер. Принцип работы RS-триггера. Схема :: SYL.ru

Место триггеров в цифровой схемотехнике

Классификация

RS-триггер на логических элементах

Состояние «Установлен»

Состояние «Сброшен»

Сводим результаты в таблицу

Состояние S R Q Q̃ Описание Установка 1 0 0 1 Выход Q̃ =1 1 1 0 1 без изменений Сброс 0 1 1 0 Выход Q̃ =0 1 1 1 1 без изменений Недопустимое 0 0 1 1 состояние ошибки Диаграмма переключения RS-триггера

Модифицируем схему триггера

Как синхронизировать работу триггера

Регистры на триггерах

Симметричные триггеры | HomeElectronics

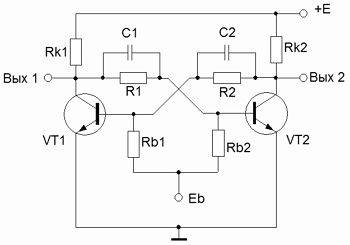

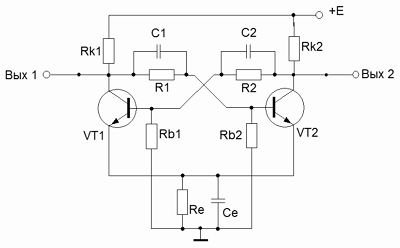

Устройство и принцип работы симметричного триггера

Схема симметричного триггера с независимым смещением.

Схема симметричного триггера с независимым смещением. Схемы запуска триггера

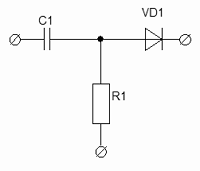

Схема запуска триггера.

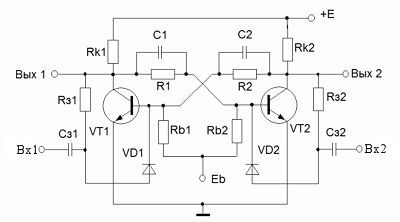

Схема запуска триггера.  Симметричный триггер с независимым смещением и раздельным запуском.

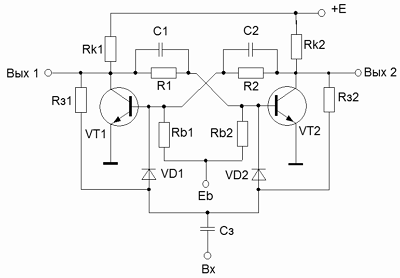

Симметричный триггер с независимым смещением и раздельным запуском.  Симметричный триггер с независимым смещением и счётным запуском.

Симметричный триггер с независимым смещением и счётным запуском. Симметричный триггер с автоматическим смещением.

Симметричный триггер с автоматическим смещением.

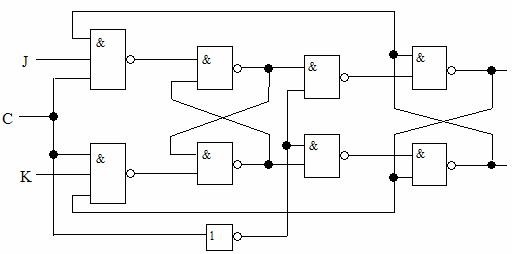

Симметричный триггер с автоматическим смещением. JK-триггер. Принцип работы, фунцкциональные схемы, таблицы истинности

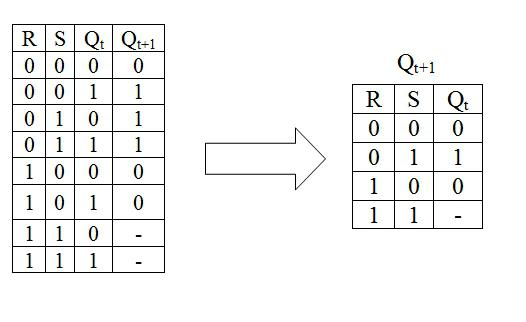

RS-триггер. Принцип работы, функциональные схемы, таблица переходов

Классифицируют триггеры по следующим признакам:

Классифицируют триггеры по следующим признакам:

Входные логические элементы И-НЕ передают переключающую логическую единицу с информационного входа S или R на необходимые входы асинхронного триггера типа RS с инверсными входами только при условии наличия на синхронном входе (С) сигнала с уровнем логической единицы.

Входные логические элементы И-НЕ передают переключающую логическую единицу с информационного входа S или R на необходимые входы асинхронного триггера типа RS с инверсными входами только при условии наличия на синхронном входе (С) сигнала с уровнем логической единицы.RS, JK, D, T, принцип действия, видео, практическое приминение / Школа электрика / Коллективный блог

Что такое триггеры?

RS-триггер

D-триггеры

JK-триггер

Т-триггер

Практическое использование триггера

3.4.Основные схемы включения триггеров

3.4.1. Подавление дребезга контактов выключателя при помощи триггера

3.4.2. Использование триггера в качестве флага процесса

схема и принцип работы :: SYL.ru

Что такое D-триггер?

Принцип работы триггера

Схематическое построение D-триггеров

Физические реализации триггерных систем

Синхронные и асинхронные триггеры: в чем разница?

Динамические и статические триггеры

Использование триггеров

интернет-магазин светодиодного освещения

Пн - Вс с 10:30 до 20:00

Санкт-Петербург, просп. Энгельса, 138, корп. 1, тк ''Стройдвор''

Поделиться с друзьями: